cadence IC系列使用(5)drc lvs 参数提取及后仿

系统:redhat 6.5

cadence IC版本:IC617

库:FreePDK15

模型:PTM-MG 7nfet 7pfet

版图验证工具:calibre(mentor)

仿真工具:hspiceD(synopsys)

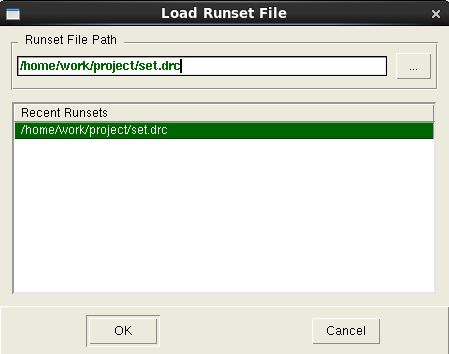

打开前面画好的版图,选择菜单栏下的 Calibre — run nmDRC,可能会出现先弹出下列的窗口。

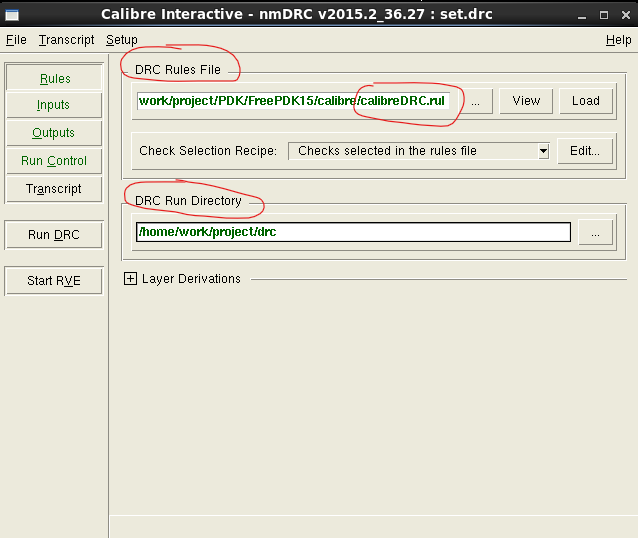

你可以自定以路径和文件名,这个主要是记录跑 DRC 时的一些设置。设置好后,点击 OK 。出现下图的设置,在 DRC Rules File 中填写 DRC 规则文件,对于 FreePDK15,文件名为 calibreDRC.rul 。由于在运行 DRC 时会产生大量的文件,这里建议单独建立一个文件夹用来存放跑 DRC 的文件,在 DRC Run Directory 中选择文件夹。这些设置都会记录到刚刚弹出的那个窗口中,你设置的文件中(最后你关闭这些窗口时会问你需不需要保存这些设置)。

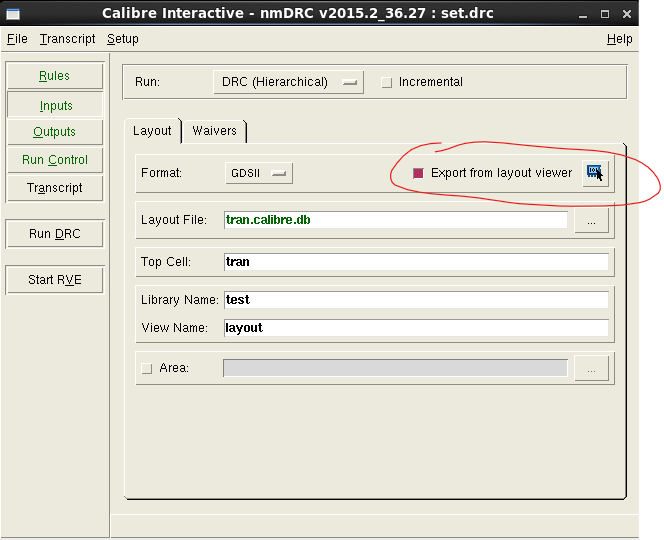

在 inputs 那栏中,主要需要勾选 Export from layout viewer 。

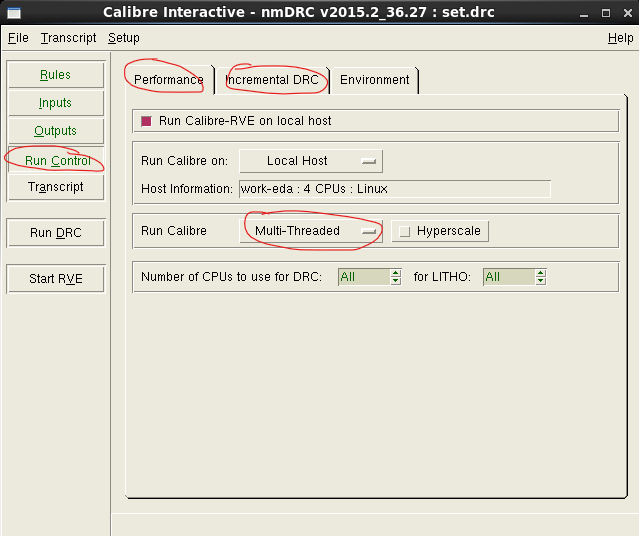

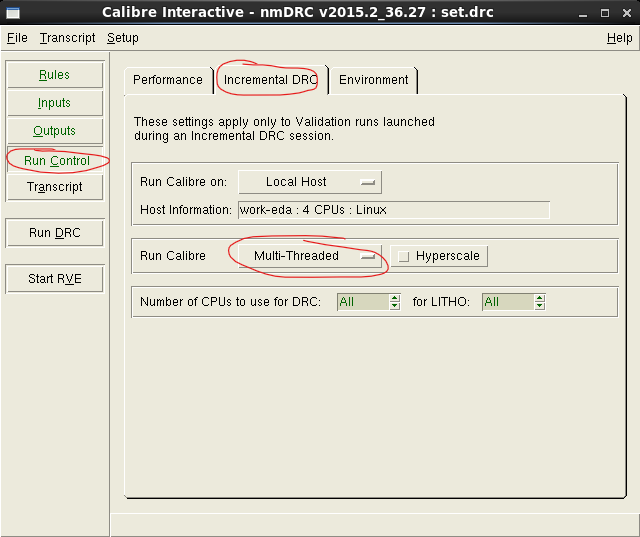

Outputs 那栏没什么东西好设置的,注意一下输出的文件名就行了。在 Run Control 那栏,主要可以利用超线程以及分布式计算加快速度,在 Performance — Run Calibre 中,可以选择 Multi-Threaded,在 Incremental DRC 中也可以做相同的设置。

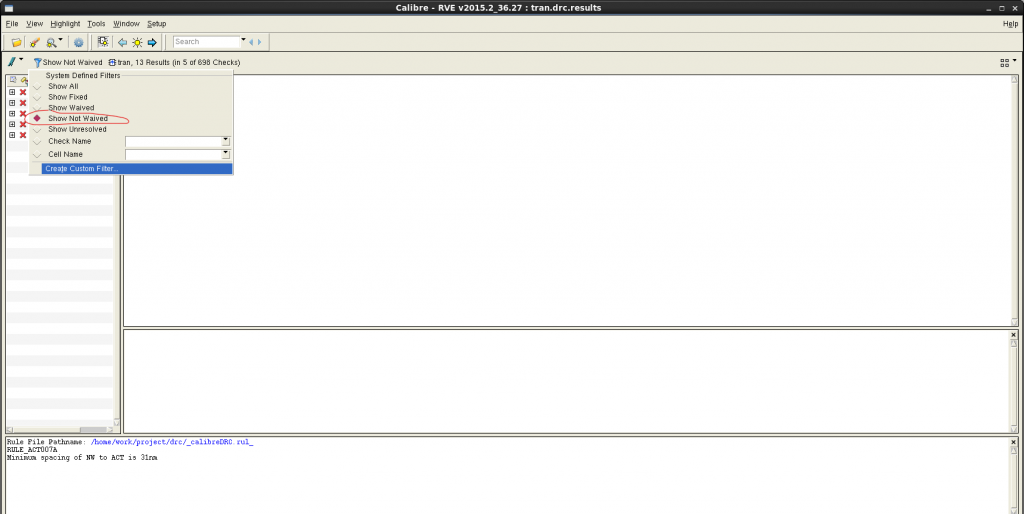

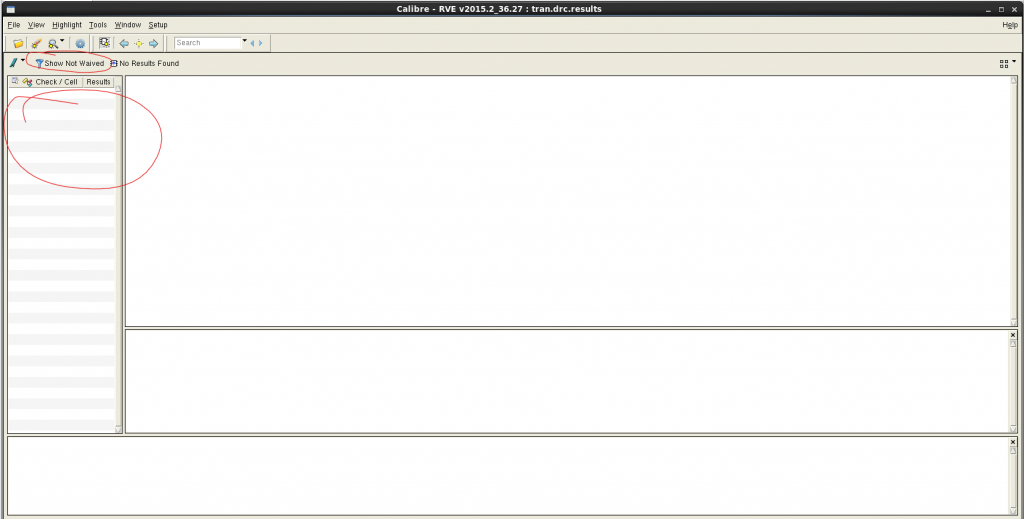

Transcript 是显示运行过程中的一些信息,设置好后,就可以点击 Run DRC 了。点击 Show Not Waived 可以查看有哪些错误。然后按照错误一个一个慢慢修改。

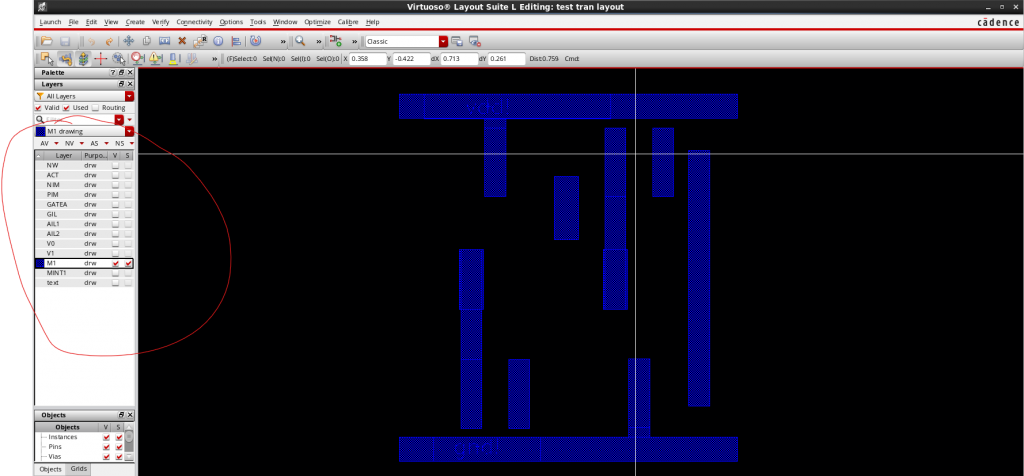

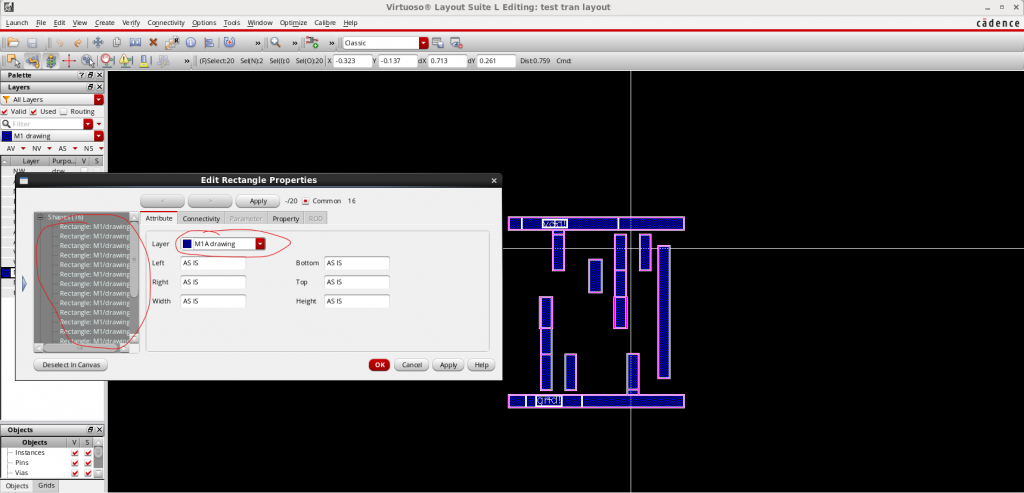

对于我画的版图,因为我最初是用的 M1A 层和 MINT1A 层画的,这两层是不进行 DRC 检查的,现在用的 M1 层和 MINT1 层画的,所以会有这么多错误,现在我将版图中所有的 M1 层都改为 M1A 层。方法如下,在版图窗口中,只显示 M1 层,

框选所有的图形,按小写的 q ,弹出属性窗口,按住 shift 键选中所有(包括 shape、pin 和 label),在 Layer 中选择 M1A Drawing ,然后点击 OK 即可,利用同样的方式将所有 MINT1 改为 MINT1A 层。

现在查看,就会发现里面使用过的层就没有了 M1 和 MINT1 。

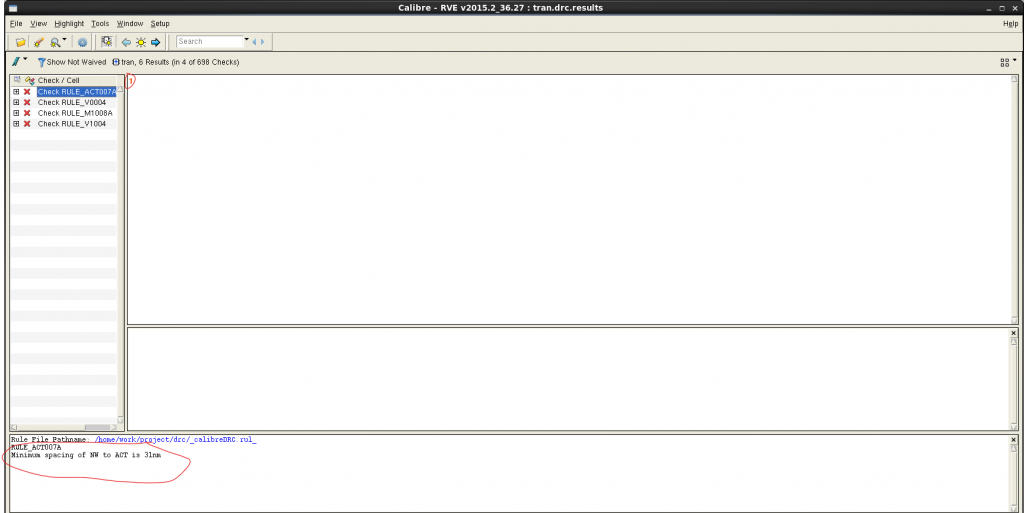

再次运行 DRC,会发现错误一下减少了好多个 。

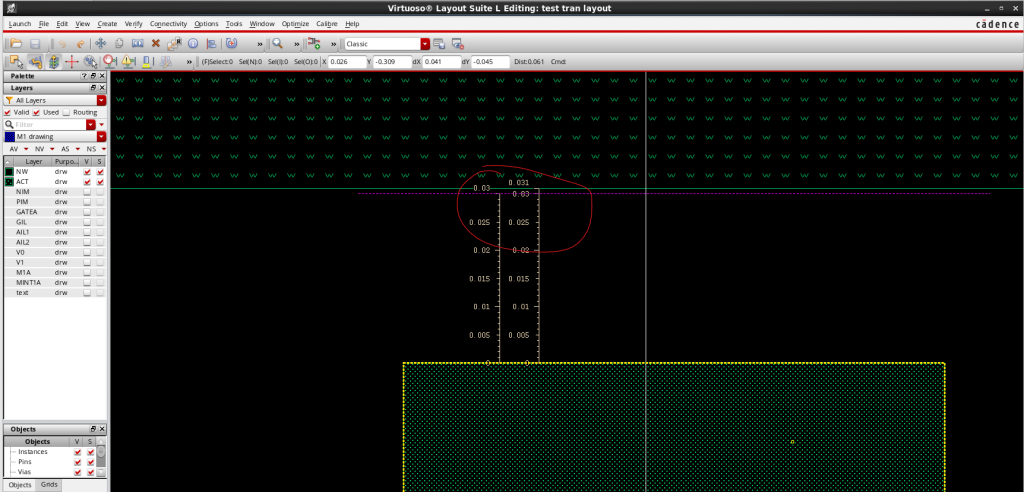

首先解决第一个错误,这是说 N 阱距离有源区最小 31 nm,我们双击错误序号 1 ,就可以在版图显示当前错误发生的位置并高亮显示(有时可能会被其它层的颜色覆盖,这是我们可以不显示一些层)。我们将 N 阱的宽缩小 1 nm ,按小写 s ,选中 N 阱的下面那条边,向上拖动 1 nm(拖动过程可以放大缩小使得准确)。

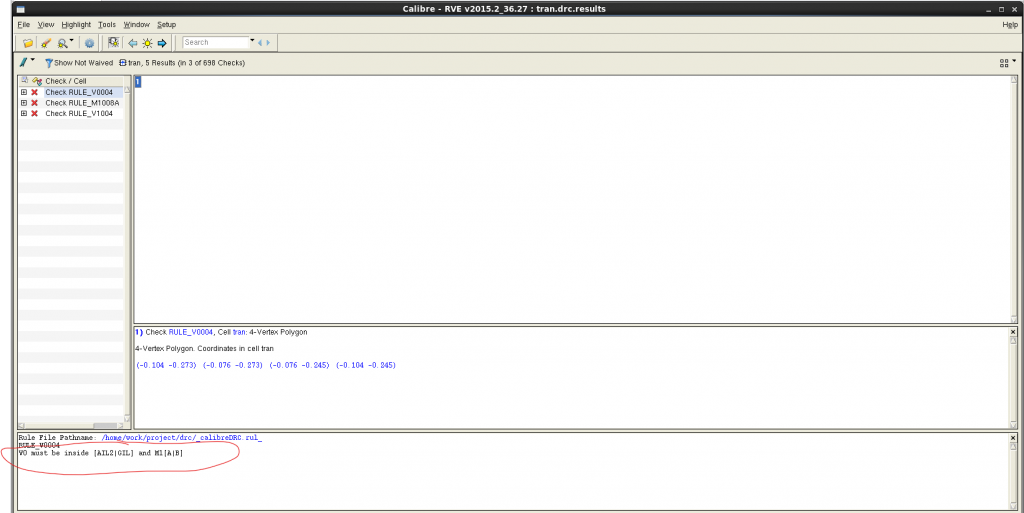

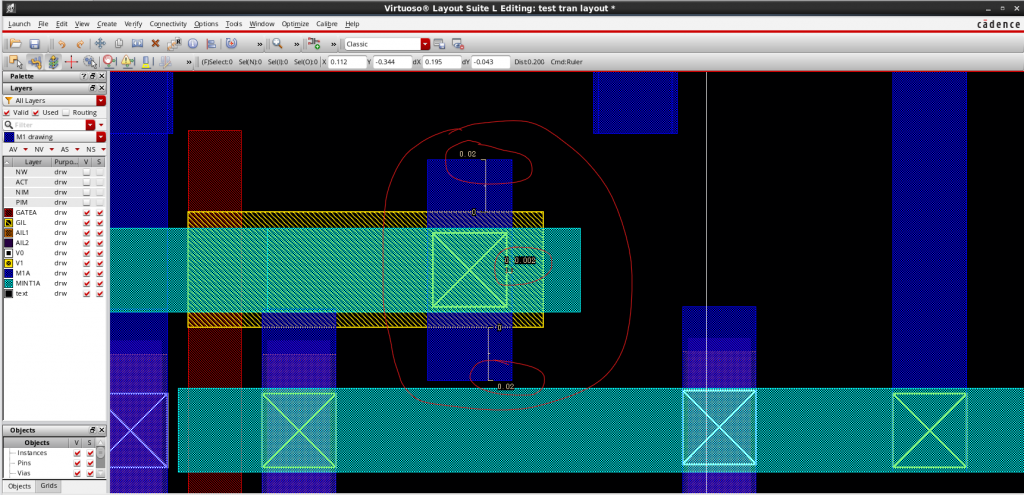

然后解决第二个错误,说是 V0 必须在 AIL2 或者 GIL 与 M1A 或者 M1B 之间。我们检查版图发现,这里缺少 M1A 层。

将其补上,注意位置。再次进行 DRC 检查,就没有发现错误了(第三个错误是由于线的宽度画错了,很容易检查出来)。

如果还有其它错误,继续修改,直到 DRC 验证通过,如下图所示,没有一个错误。如果有错误没有修改的话,后面 LVS 是不会通过的,因为 LVS 验证时会首先进行 DRC 验证(从 LVS 规则文件可以看出来)。

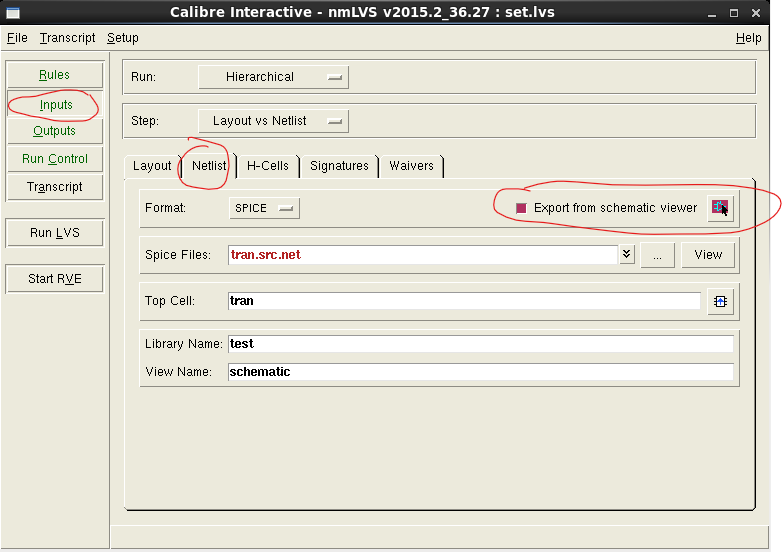

然后进行 LVS 验证,点击菜单栏下的 calibre — run nmLVS,参考 DRC 的设置,可以单独设置一个文件夹来保存 LVS 验证时产生的大量文件,同样,在 Outputs 和 Run Control 中可以做跟 DRC 类似的设置。需要注意的是,在 input 中 ,需要勾选 Netlist 下方的 Export from schematic viewer 。然后就可以点击 Run LVS 了。

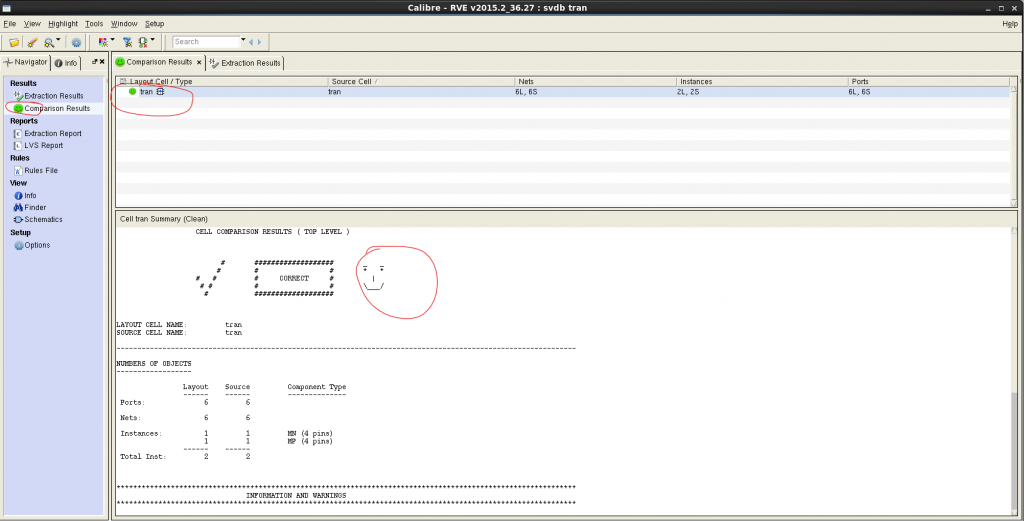

如果出现笑脸,就证明 LVS 通过了。如果没有通过,则需要仔细检查,特别留意有没有哪些地方的连线忘记画了,因为版图一旦复杂起来,如果自己手动布线的话,很容易少画连线或者连线不对,有时一根错误的连线可能会导致好几十个错误甚至更多。

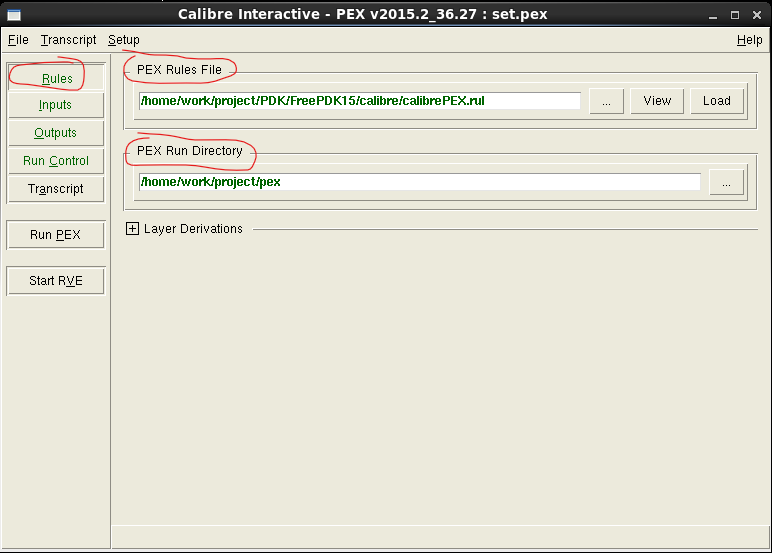

然后是参数提取,点击 Calibre — Run PEX ,选择规则文件位置(calibrePEX.rul)以及在参数提取时生成大量文件保存的位置。

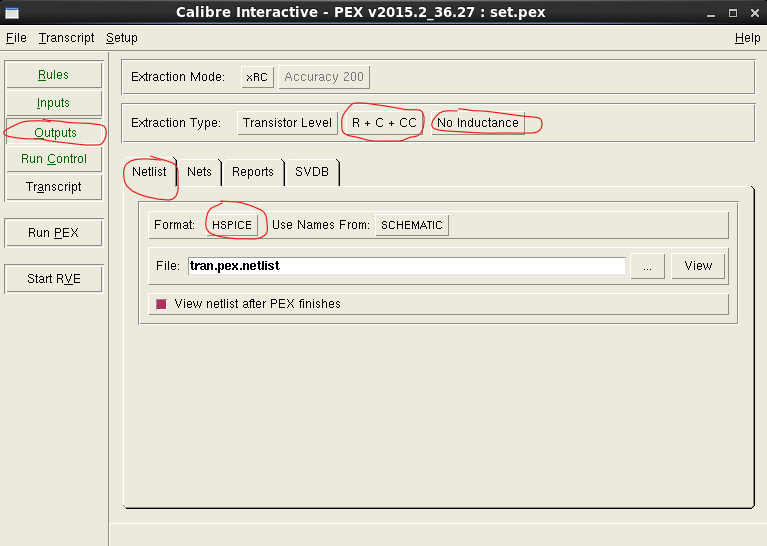

input 中 netlist 栏同样需要勾选 Export from schematic viewer,在 Outputs 中,可以选择提取参数类型,R为寄生电阻,C为寄生电容,CC为线间寄生电容。当然还可以提取自感互感这些。在这里我选择提取网表的格式为 HSPICE ,在 Run Control 中同样可以设置多线程运行加快速度。在参数提取时会首先进行 LVS 验证(从规则文件可以看出来),因此如果 LVS 验证不通过的话,是无法进行参数提取的。点击 Run PEX 开始参数提取。

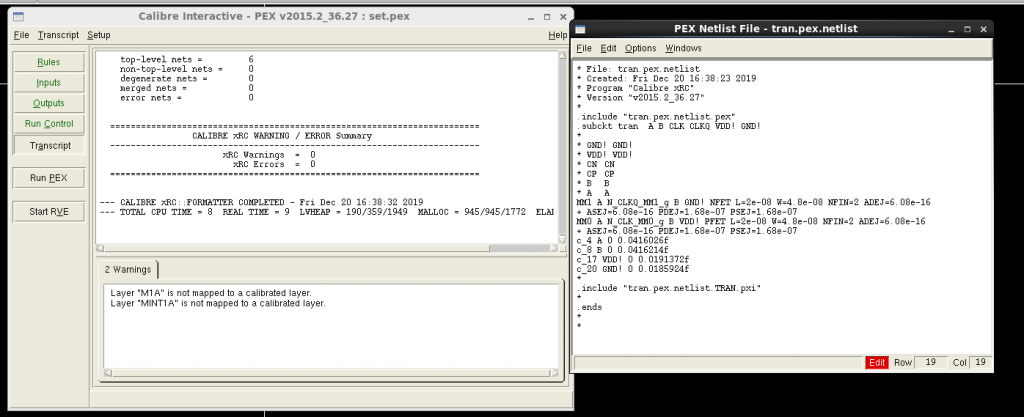

参数提取完成,没有错误,有两个警告。

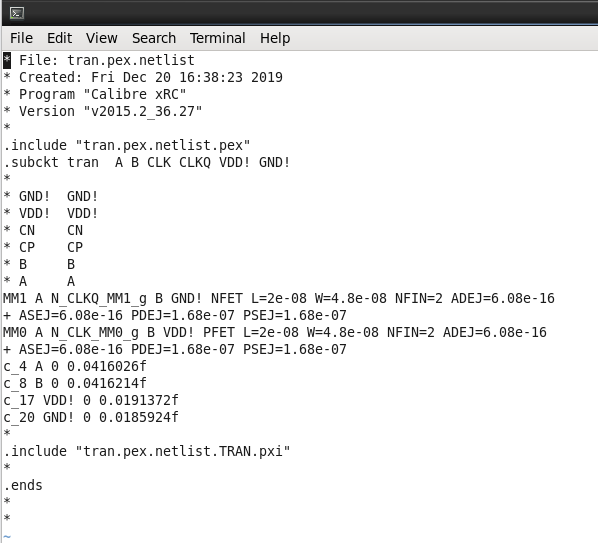

只要在你设置的目录中生成了 *.pex.netlist 、*.pex.netlist.pex 和 *.pex.netlist.*.pxi 就表示参数提取是成功的。有可能也只有其中两个文件,这是跟你提取参数的类型有关的。其中 *.pex.netlist 是主网表文件,*.pex.netlist.*.pxi 是提取的线间寄生电容,*.pex.netlist.pex 是将提取的电容电阻组合成分布RC电路。提取的网表根据版图将电路重新描述了出来,下图是提取的主网表的内容。

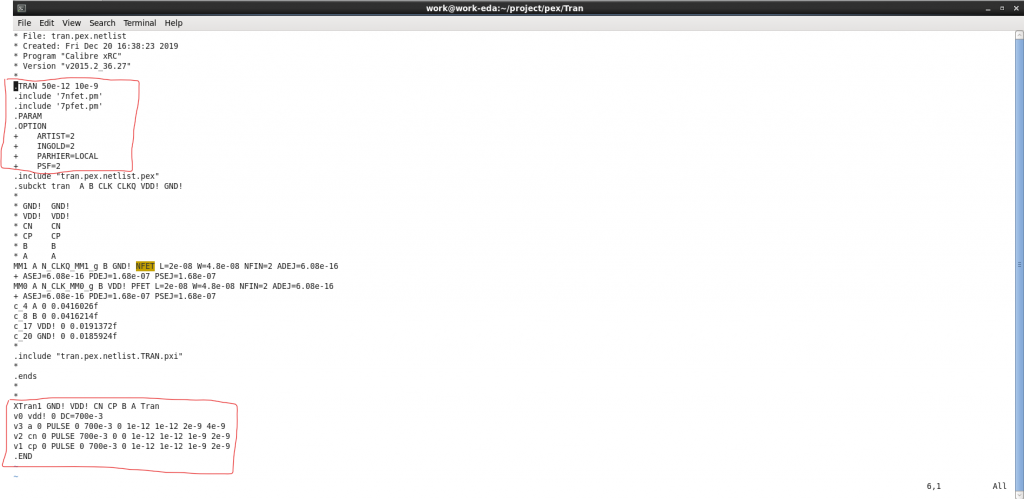

现在这样是不能进行后仿真的,因为我们没有添加激励,任然需要修改网表,只需要懂一点网表 的知识就可以了。第一部分代码为

.include '7nfet.pm'

.include '7pfet.pm'

.PARAM

.OPTION

+ ARTIST=2

+ INGOLD=2

+ PARHIER=LOCAL

+ PSF=2第二段代码如下

XTran1 A B CP CN VDD! GND! Tran

v0 vdd! 0 DC=700e-3

v3 a 0 PULSE 0 700e-3 0 1e-12 1e-12 2e-9 4e-9

v2 cn 0 PULSE 700e-3 0 0 1e-12 1e-12 1e-9 2e-9

v1 cp 0 PULSE 0 700e-3 0 1e-12 1e-12 1e-9 2e-9

.END最终的主网表如下图所示

需要将模型文件 7nfet.pm 和 7pfet.pm 复制到当前文件夹,然后运行

hspice -i tran.pex.netlist如果没有错误,将会生成以 tr0 结尾的波形文件。使用下列命令查看波形。

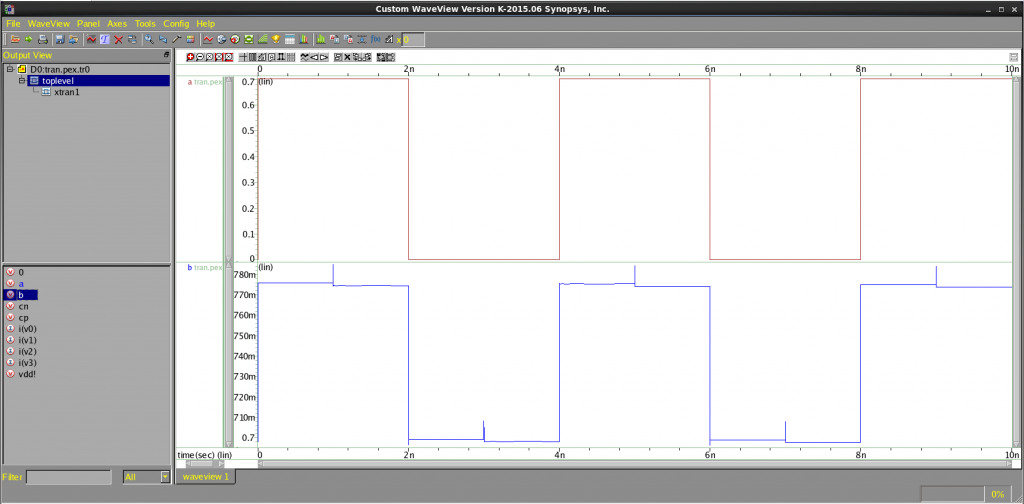

wv tran.pex.tr0最终波形如下图所示,至此,后仿真完成。

如果在这个过程中遇到了其它问题,欢迎在评论区留言,或者Google一下,也欢迎把具体的解决方法留在评论区,以供后来者参考

感谢您的支持,请扫码打赏