cadence IC系列使用(3)–前仿真

系统:redhat 6.5

cadence IC版本:IC617

库:FreePDK15

模型:PTM-MG 7nfet 7pfet

版图验证工具:calibre(mentor)

仿真工具:hspiceD(synopsys)

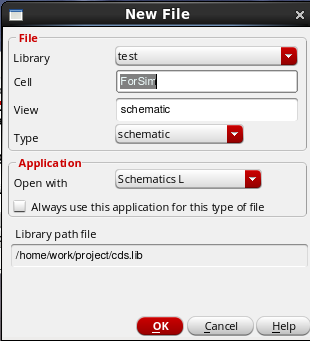

首先新建一个测试电路,在 Linux 的终端 virtuoso & 打开 cadence IC 617,点击 File — New — Cellview ,在弹出的框中选择 Library 为 test ,Type 为 schematic ,Cell 为 ForSim(这个任意)。

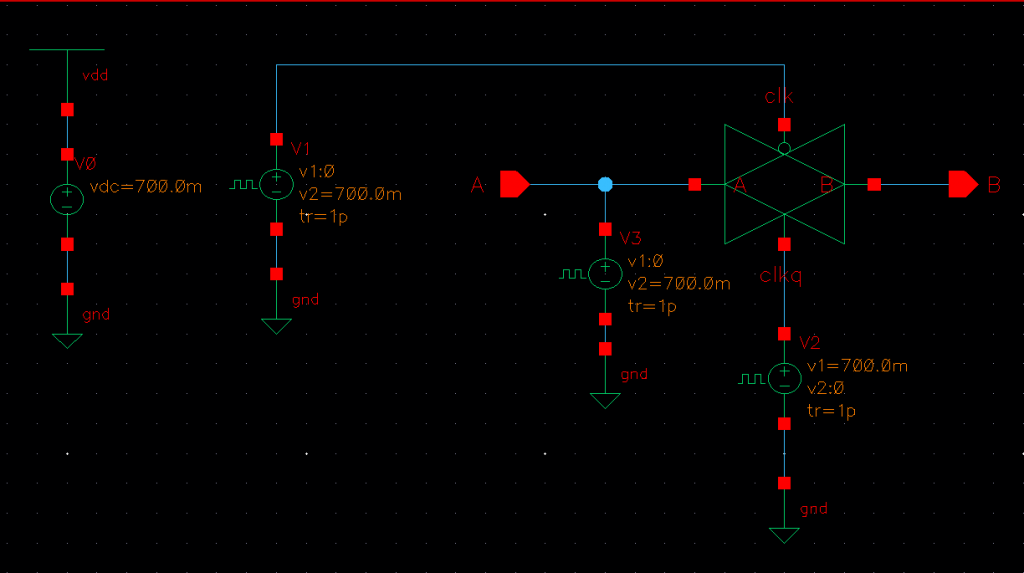

然后建立如下的测试电路,在库 analogLib 中可以找到 vdc (直流电压)和 vpulse (脉冲电压)。

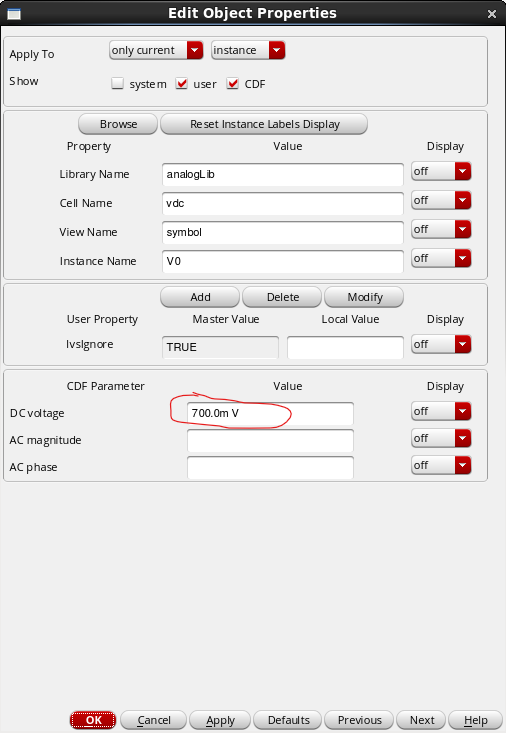

其中各个电压的参数如下图所示,从左往右 ,v0 为 vdc , 只需要设置 DC voltage 为 0.7 即可,软件默认单位电压单位为 V 。

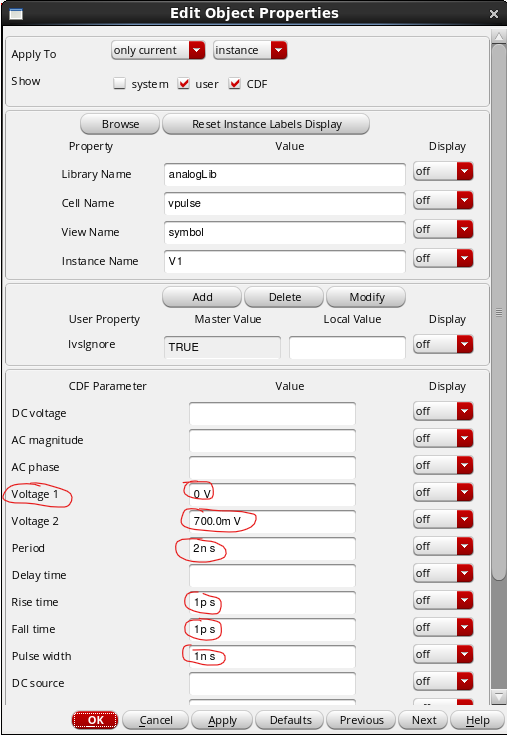

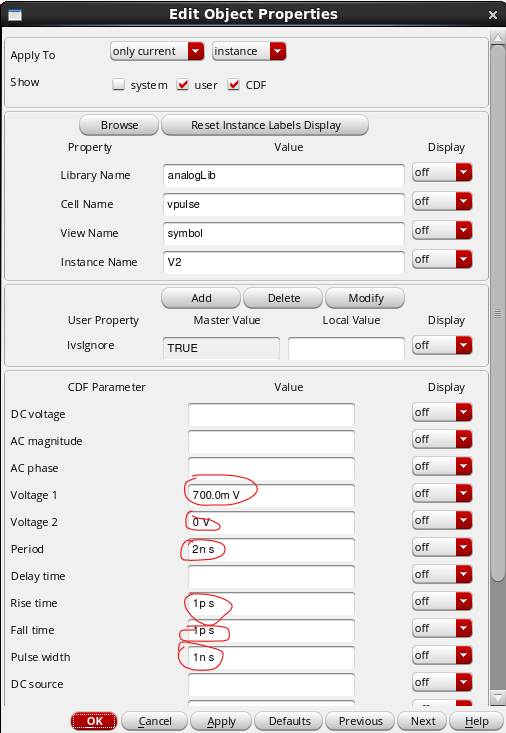

v1 为 vpulse ,设置 Voltage 1 为 0 ,Votltage 2 为 0.7,Period 为 2n (软件默认时间单位为秒), Rise time(上升时间) 为 1p , Fall time (下降时间)为 1p ,Pulse width 为 1n ,这样相当于设置了一个占空比为 50% 的方波,其高电平为 0.7v ,宽度为 1ns ,低电平为 0v ,宽度为 1ns 。

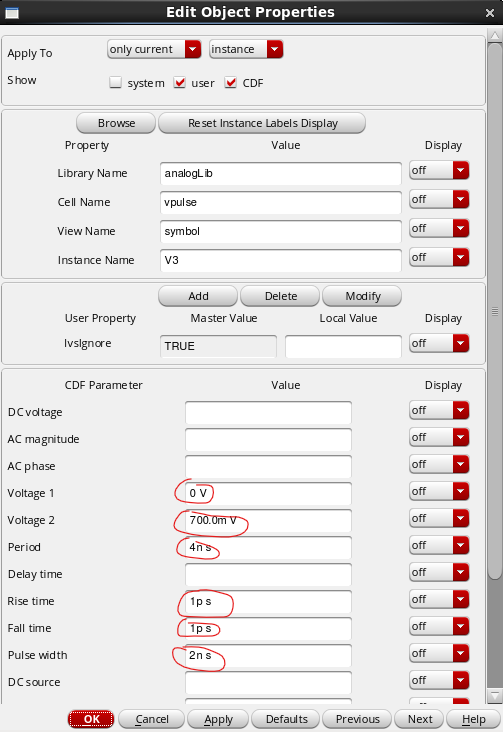

v3 为 vpulse , Voltage 1 为 0 ,Votltage 2 为 0.7,Period 为 4n , Rise time 为 1p , Fall time 为 1p ,Pulse width 为 2n 。

v2 为 vpulse ,因为 v2 所接的端口为 clk 非,这里没有画反相器,所以可以像如下设置使得与clk的信号相反。只需要将 Voltage 1 设为 0.7 ,Voltage 2 设为 0 即可。

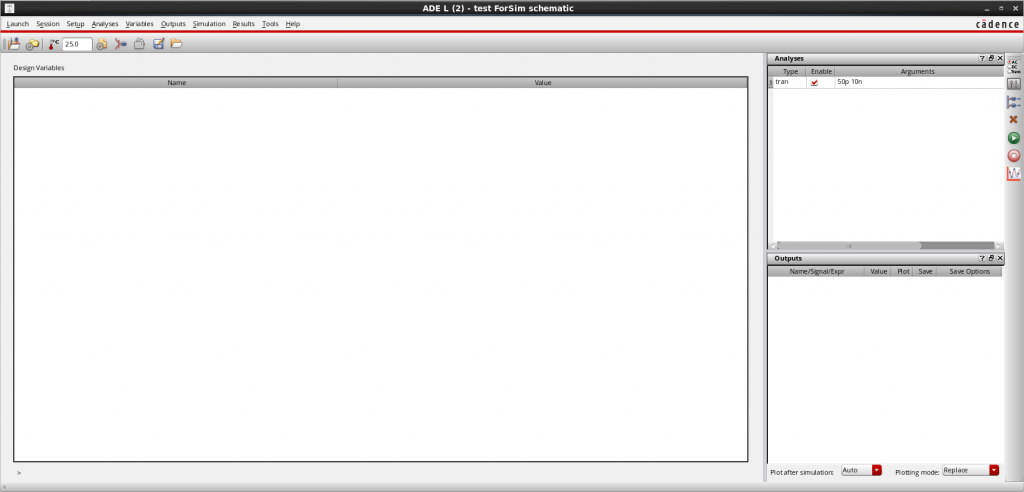

点击菜单栏的 Launch — ADE L ,弹出下面的窗口

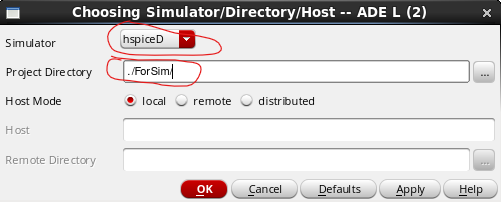

点击 Setup — Simulator/Directory/Host ,在弹出的窗口中,设置 Simulator 为 hspice D ,Project Directory 任意,后面生成的网表在这个文件夹中,点击 OK。

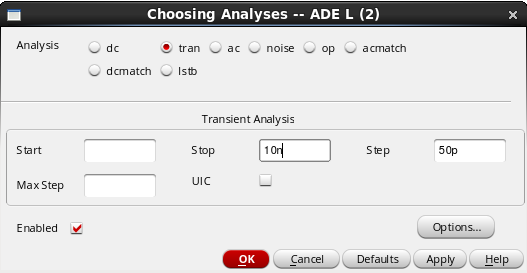

点击 Analysis — choose,弹出下面的对话框,设置 stop 为 10n (仿真结束时间),步长 Step 为 50p ,这个视实际情况而定,点击 OK。

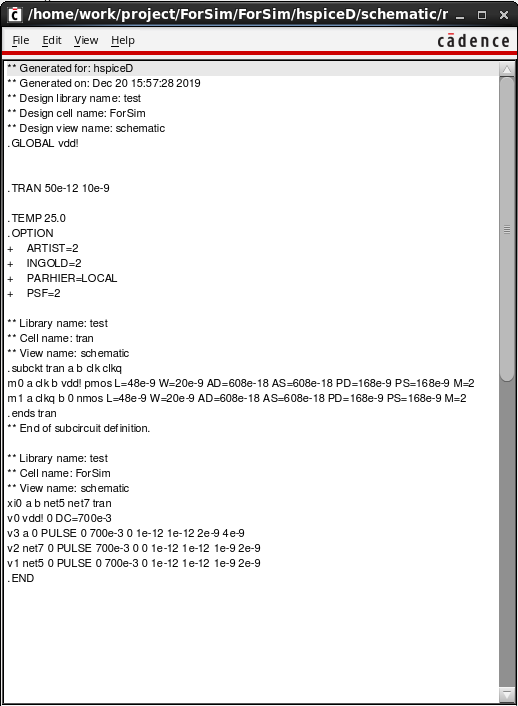

点击 Simulation — Netlist — create,会弹出生成的网表,同时也会保存在刚才你设置的目录下。文件名为 input.ckt 。下图为生成的网表内容。

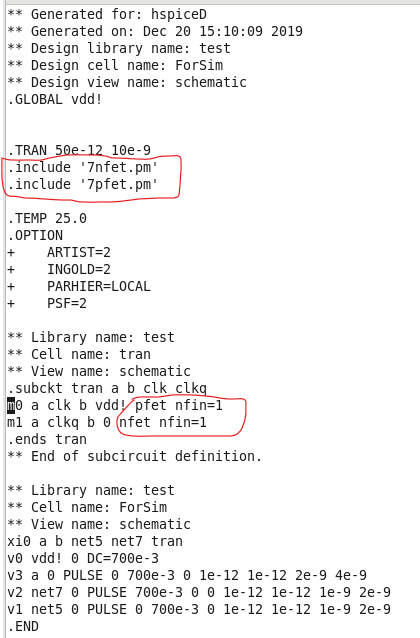

这个网表还不能用的,因为我们没有设置任何模型,需要对这个文件进行一些简单的修改。首先把模型文件包含进来,只需要添加两行代码即可,如果你像我这样写的话,模型文件需要跟你的网表文件在同一个文件夹里面。

.include '7nfet.pm'

.include '7pfet.pm'并将晶体管 m0 和 m1 的性质做一些更正,首先 m0 和 m1 都是鳍式场效应晶体管,其次 nfin 都设置为 1 ,最终如下图所示。

当然如果你会写网表的话,可以不用 cadence 生成。接下来在 Linux 的 终端中输入下面的命令进行仿真(现在你的当前文件夹下至少应该有 7nfet.pm、7pfet.pm 和 input.ckt 这三个文件)。

hspice -i input.ckt如果没有任何错误,将会生成 input.tr0 的波形文件。使用下列命令打开生成的波形文件。

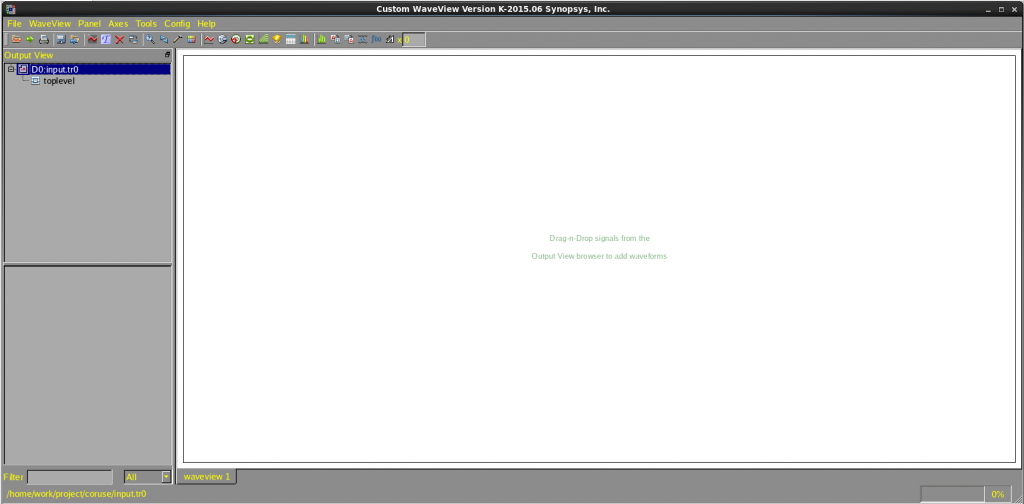

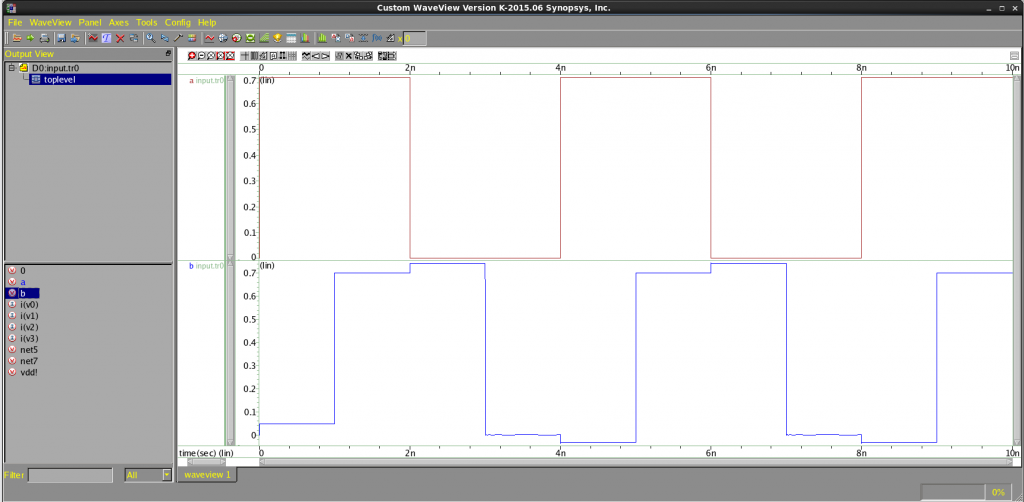

wv input.tr0如下图所示

点击 D0:input.tro — toplevel,然后双击 a 和 b 便可查看输入,输出波形,出现这种情况是正常的,因为传输门本身是有延迟的,至此,前仿真完成。

如果在这个过程中遇到了其它问题,欢迎在评论区留言,或者Google一下,也欢迎把具体的解决方法留在评论区,以供后来者参考

欢迎转载,不需注明出处,就说是你写的

感谢您的支持,请扫码打赏