⇦

有序集 – Ordered Sets

Ordered Sets 用于两个设备物理层之间的通信。

Gen1/2 总是以字符 COM 开头。用于链路训练,时钟补偿和改变链路功耗状态。

有序集分为TSOS(包括TS0OS,TS1OS和TS2OS,也简称为TS0,TS1,TS2),SKPOS,EIOS,EIEOS,FTSOS和SDSOS

Training Sequences(简称TS)用于初始化位锁定、字符锁定和交换PL层参数。

在 2.5 GT/s 和 5.0 GT/s 时, TS不会加扰,在8.0 GT/s以及以上时,可能会加扰也可能不会加扰。

TS有3类:TS0, TS1和TS2。TS是连续传送,但是中间可以插入 SKP Ordered Sets(简称SKPOS)或者EIEOS Ordered Sets(针对2.5 GT/s 以上,因为 EIEOS 在 5.0 GT/s 及以上才有)

TS0OS每个符号的含义

符号

gen1-gen5

支持Standard SKPOS(Non-Flit)

0,8

无

TS0标识符

1,9

无

EQ Byte0

2,10

无

EQ Byte1

3,11

无

EQ Byte2

4,12

无

EQ Byte3

5,13

无

EQ Byte4

6,14

无

EQ Byte5

7,15

无

用于DC平衡或奇偶检验

TS0 symbol 0,8 – TS0标识符,未加扰的33h

Bits 7,5,3,1 : 0101b

Bits 6,4,2,0 : Half Scrambling前的值不重要,在经过Half Scrambling之后跟bits 7,5,3,1相同

TS0 symbol 1,9 – Equalization Byte 0 – Half Scrambled

symbol 1决定了symbol 2到6的含义

symbol 9决定了symbol 10到14的含义

Bits 3,1 Equalization Control (EC)

00b Phase0(用在Phase 0 和 Phase 1)

01b Phase1(用在Phase 0 和 Phase 1)

10b Phase2(Upstream Lane用在Phase 2,Downstream Lane只用在初始请求Upstream Lane向Phase 2移动)

11b Phase3(只用在Upstream Lane初始请求Downstream Lane进入Phase 3)

Bit 5 : Reset EIEOS Interval Count – 在Recovery.Equalization Phase 2使用,其它状态保留

0b : 不复位EIEOS内部计数

1b : 复位EIEOS内部计数

Bit 7 : Use Preset – 在Recovery.Equalization Phase 2和3有定义,在USP Phase 3和DSP Phase 2改比特是0b,其它状态保留

0b : 使用Coefficients

1b : 使用Preset

Bits 6,4,2,0 – Half Scrambling前的值不重要,在Half Scrambling之后,跟Bits{7,5,3,1}相同

TS0 symbol 2,10 – EQ Byte1

Equalization Byte 1 – Half Scrambled

对当前速度而言,取决于symbol 1或者9的EC字段

Bits 7,5,3,1 :

Phase 0 & 1 FS[3:0]

Phase 2 & 3 当Use Preset字段是0b是,第一个Pre-Cursor Coefficient(C-1 )

其它状态 : 保留

Bits 6,4,2,0 – Half Scrambling前的值不重要,在Half Scrambling之后,跟Bits{7,5,3,1}相同

TS0 symbol 3,11 – EQ Byte2

Equalization Byte 2 – Half Scrambled

对当前速度而言,取决于symbol 1或者9的EC字段

Bits 3,1

Phase 0 & 1 : FS[5:4]

Phase 2 & 3 : 当Use Preset字段位0b时,Post-Cursor Coefficient(|C+1 |)

其它状态,保留

Bits 6,4,2,0 – Half Scrambling前的值不重要,在Half Scrambling之后,跟Bits{7,5,3,1}相同

TS0 symbol 4,12 – EQ Byte3

Equalization Byte 3 – Half Scrambled

对当前速度而言,取决于symbol 1或者9的EC字段

Bit 1

Phase 0 & 1 : LF[2]

Phase 2 & 3 : 当Use Preset字段位0b时位Post-Cursor Coefficient(|C+1 |)

其它状态 : 保留

Bits 7,5,3

Phase 0 & 1 LF[5:3]

Phase 2 & 3 当Use Preset字段位0时,表示Second Pre-Cursor Coefficient(|C-2 |)

其它状态 : 保留

Bits 6,4,2,0 – Half Scrambling前的值不重要,在Half Scrambling之后,跟Bits{7,5,3,1}相同

TS0 symbol 5,13 – EQ Byte4

Equalization Byte 4 – Half Scrambled

对当前速度而言,取决于symbol 1或者9的EC字段

Bits 7,5,3,1

Phase 0 & 1 : Transmitter Preset

Phase 2 & 3 : 如果Use Preset为1表示Transmitter Preset

其它状态保留

Bits 6,4,2,0 – Half Scrambling前的值不重要,在Half Scrambling之后,跟Bits{7,5,3,1}相同

TS0 symbol 6,14 – EQ Byte5

Equalization Byte 5 – Half Scrambled

对当前速度而言,取决于symbol 1或者9的EC字段

Bits 3,1

Phase 2 & 3 : 当Use Preset字段为1时表示Cursor

其它状态保留

Bit 5 : Retimer Equalization Extend

Bit 7 : 保留

Bits 6,4,2,0 – Half Scrambling前的值不重要,在Half Scrambling之后,跟Bits{7,5,3,1}相同

TS0 symbol 7,15 – 直流平衡/奇偶校验

如果在TS0开始的时候需要调整DC Balance, 00-FFh未加扰

否则,Bits 7,5,3,1

Byte级别偶校验 – Half Scrambling

Symbol 7 = Symbol 0 ^ Symbol 1 ^ … Symbol 6

Symbol 15 = Symbol 8 ^ Symbol 9 ^ … Symbol 14

Bits 6,4,2,0 – Half Scrambling前的值不重要,在Half Scrambling之后,跟Bits{7,5,3,1}相同

16个symbol,只在1b/1b编码下有

只有Recovery.Equalization会用到

16个 symbol,每一个 symbol 有 8bits,代表不同的意思

TS1OS每个符号作用

符号

gen1/2

gen3/4/5

gen6

0

TS1标识符(COM)

TS1标识符(1Eh)

1Bh

1

链路号

链路号

Link number/EQ Byte 0

2

lane号

lane号

Lane number/EQ Byte 1

3

N_FTS

N_FTS

EQ Byte 2

4

速度标识

速度标识

EQ Byte 3

5

链路控制

链路控制

速度标识

6

标准TS1OS/Compliance TS1OS/EQ TS1OS

EQ相关

链路控制

7

TS1标识符(D10.2,4Ah)

EQ相关参数

直流平衡或者奇偶检验位

8

TS1标识符(D10.2,4Ah)

EQ相关参数

同symbol 0

9

TS1标识符(D10.2,4Ah)

EQ相关参数/校验位

同symbol 1

10-13

TS1标识符(D10.2,4Ah)

TS1标识符(4Ah)

symbol 10/11/12/13分别同symbol 2/3/4/5

14-15

TS1标识符(D10.2,4Ah)

TS1标识符(4Ah)/DC平衡

symbol 14/15分别同symbol 6/7

TS1 Symbol 0

8b/10b编码

8b/10b编码时,在2.5或者5.0 GT/s时,为COM(K28.5)字符,用来实现符号对齐

128b/130b编码

128b/130b编码时,在8.0 GT/s及以上时,固定编码为1Eh(8’b0001_1110),标识这是一个 TS1 而不是其它,在 Gen3 及以上时,没有 8b/10b 编码来维持 DC (直流) 平衡,所以在一些固定编码上会尽量保持 0 和 1 的个数相当。

1b/1b编码时

编码为1Bh

TS1 Symbol 1 – Link Number(链路号)/EQ Byte0

Q : 在1b/1b编码时,在有些状态并不是表示Link Number,那么在连续TS的判断中,如何判断Link Number是连续的呢?

A : 在这些状态,虽然不表示Link Number,但是在这些状态Link Number已经协商好,默认前面没问题时,Link Number就是连续的,而在某些状态,比如Configuration时,需要用到Link Number,此时就必须表示为Link Number。后面的Lane Number同理

TS1 Symbol 1

8b/10b编码

端口不支持8.0 GT/s及以上时,取值为0-255或者PAD(K码)

128b/130b编码

支持8.0 GT/s及以上的Downstream port时,取值为0-31或者PAD. 此处可能是因为gen3及以上的RC受电气参数的影响,无法使用更多的链路

支持8.0 GT/s及以上的Upstream port时,取值为0-255或者PAD

1b/1b编码时

表示为Link Number ,需要加扰,只有在Configuration,hot reset和Recovery.RcvrCfg时才表示为Link Number,取值为0-31和PAD(F7h)。接收机在Recovery.Idle时,只会检查这个symbol是否为PAD

在Recovery和Loopback时表示为EQ Byte 0Recovery.Equalization和Loopback.Entry中使用,在Recovery的其它状态,为00b,在Loopback其它状态保留Recovery.Equalization中用,在LTSSM其它状态保留Recovery.Equalization,Recovery.RcvrLock和Loopback中使用,在其它状态保留

TS1 Symbol 2 – Lane Number(链路的通道号)/EQ Byte1

TS1 Symbol 2

8b/10b编码

当链路速度在2.5或者5.0 GT/s时,取值为0-31或者PAD(K23.7)

128b/130b编码

当链路速度在8.0 GT/s或者更高时,取值为0-31或者 PAD(F7h)

1b/1b编码时

在Configuration和Hot Reset时表示为Lane number,需要加扰Recovery.Idle时只会检查该symbol是否为PAD

在Recovery和Loopback.Entry表示为EQ Byte 1,需要加扰,其它状态保留0 |Recovery使用,在Loopback.Entry保留)Recovery中使用,在Loopback.Entry保留)

TS1 Symbol 3 – N_FTS/EQ Byte2

TS1 Symbol 3

8b/10b编码或者128b/130b编码

接收机需要的Fast Training Sequences(简称 FTS)数量,取值范围为0-255.在Flit模式保留

1b/1b编码

在Recovery和Loopback.Entry表示为EQ Byte 2,需要加扰,其它状态保留-1 |-2 |Recovery.Equalization中设置为1,在Recovery的其它状态必须设置为1

TS1 Symbol 4 – 数据指示标志/EQ Byte3

note : 正常训练在第一次进入configuration.LinkWidth.Start时不允许设置bit[5:1]为10111b ,但是在loopback测试时例外,因为需要在此状态协商速度。

TS1 Symbol 4

8b/10b编码或者128b/130b编码

bit[0] : 是否支持Flit模式,Gen6新增,在Gen5及以前保留

bit [5:1] 支持的链路速度,Non-Flit Mode 编码如下Polling.Active,Configuration.Linkwidth.Start,Recovery.Equalization和Loopback。Polling状态以来,组件在Polling和Configuration状态传输的TS1中Supported Links Speeds为1 1111b,那么支持2.5,5.0,8.0,16.0,32.0和64.0GT/s。第一次进入configuraiotn.LinkWidth.Start发送的编码应该是11111b(支持32.0GT/s以及以上)

bit[6] : Autonomous Change/Selectable De-emphasis这种多功能位在不同的状态代表不同的作用,比如在 Recovery 状态不会有 De-emphasis 操作,因此只能是 Autonomous Change , Upstream Port 如果想改变链路带宽, 则必须把 TS2 中的 Autonomous Change 位 置 1Polling.Active, Configuraton.Linkwidth.Start和Loopback.Entry状态使用,其它状态保留Polling.Active, Configuration,Recovery和Loopback.Entry状态使用,其它情况保留

bit[7] : speed_change/SRIS ClockingConfiguration和Loopback.Entry状态,当LinkUp=0,如果该位为1,表明链路将会工作在SRIS时钟,0表示要么工作在common clocking,要么工作在SRNS时钟模式。DSP会使用该bit跟Retimer(s)沟通,确定Retimer会使用的时钟模式,LinkUp为1时在configuration和Loopback也是保留。在LTSSM中Recovery.RcvrLock状态为speed_change,其它状态保留Recovery.RcvrLock,在其它ltssm状态保留

1b/1b编码

EQ Byte 3 : 只会在Recovery和Loopback.Entry中使用,在其它状态保留,需要加扰+1 )|

TS1 Symbol 5 – 链路控制/速度标识符

TS1 Symbol 5

8b/10b编码或者128b/130b编码

链路控制 Deassert 可以理解为不执行相应动作,Assert 可以理解为执行相应动作,比如bit[0]为1时,表明需要进入Hot Reset

bit[0] : Hot Reset 位

bit[1] : Disable Link 位

bit[2] : Loopback 位

bit[3] : 禁止加扰位 (适用于 2.5 和 5.0 GT/s)

bit[4] : Compliance Receive 位(2.5 GT/s 可选,5.0 GT/s 及以上必须实现)

bit[5] : 在Loopback发送 Modified Compliance Pattern, 在 32.0 GT/s 及更高速度中的 Loopback master 中使用,其它情况保留

bit[7:6] : 增强链路行为控制bit[7:6] 只会在下面两种条件下才会定义,其它情况保留 Polling或者Configuration状态Loopack且只能是 Loopback Master编码如下:

1b/1b编码

速度标识 – 需要加扰

bit[0] : 保留

bit[5:1]

bit[6]Configuration.Linkwidth.Start和Loopback.Entry有定义,在其它状态保留Configuration,Recovery和Loopback.Entry使用,其它状态保留

bit[7]Recovery状态为1,在LTSSM其它所有状态保留

TS1 Symbol 6 – Standard TS1/Compliance TS1/EQ TS1/链路控制

TS1 Symbol 6

8b/10b编码

当链路速度在2.5 或者 5.0 GT/s 时

如果是标准的 TS1, 编码为 D10.2 (4Ah),作为 TS1 的标识符

如果是Compliance TS1OS ,bit[7:0]编码为Compliance Setting Number,即进入Polling.Compliance的次数

如果是 EQ TS1 (当需要切换到 8.0 GT/s 或者 32.0 GT/s 及以上时会有EQ过程,这时发送的 TS1 为 EQ TS1)2.5 或者 5.0 GT/s往上切换速度时,不会直接切换到 16.0GT/s,在 Gen5 时规定了可以做一次 EQ 直接切换到最高速度,所以会有下面 32.0 GT/s 及更高时的 EQ 过程

当链路速度为 8.0 GT/s 时的 EQ 过程(比如 5.0 GT/s 往 8.0 GT/s 切换时,先将连链路速度切换到 8.0 GT/s,然后看能否实现 Symbol Lock (符号锁定), 然后就会做 EQ)

当链路速度为 32.0 GT/s 是的 EQ 过程

128b/130b编码

当链路速度为8.0GT/s 及更高时

bit[1:0] : 均衡控制 (Equalization Control, 简称EC), 这些位只会在在LTSSM中的Recovery.Equalization和Loopback状态使用, 在 LTSSM 的其它状态,固定为 00b

bit[2] : 重置 EIEOS 间隔计数。这一位只会在 LTSSM中的Recovery.Equalization状态使用,LTSSM 的其它状态中保留

bit[6:3] : 发射机预设

bit[7] : 使用预设/重做 EQ。这一位在 LTSSM 中的Recovery.Equalization、Recovery.RcvrLock和Loopback状态使用,其它状态保留。这种多功能位,在不同的状态过程会有不同的含义

1b/1b编码

链路控制,在Recovery.RcvrCfg,Disable,Hot Reset或者Loopback状态使用,需要加扰

bit[3:0]

bit[7:4] : 保留

TS1 Symbol 7 – TS1标识符/EQ参数/直流平衡/奇偶校验

Q : 1b/1b编码时,symbol 7 即可以用于直流平衡,也可以用于奇偶校验,那有可能计算出来的校验为00h或者FFh吗?如果是的话,那此时怎么区分是用于直流平衡呢还是用于校验呢?

会出现计算出来的校验为00h或者ffh,个人觉得是不会的,因为Symbol 0 到 Symbol 6的值并不是任意取的,其取值很有限,如果不限麻烦,可以写个程序把所有的组合列出来,看是否可能计算的校验为00h或者ffh。

TS1 Symbol 7

8b/10b编码

当链路速度在2.5 或者 5.0 GT/s 时,为TS1 的标志,固定编码为 D10.2 (4Ah)

128b/130b编码

当链路速度在 8.0 GT/s 及以上时

bit[5:0] : 当 Symbol 6 的 EC 域为 01b 时,此位为 FS,其它情况代表当前链路速度对应的 Pre-cursor 系数

bit[6] : 发射机 Precoding (预编码) 开启,只会在 32.0 GT/s 及更更高速度下的Recovery状态使用,其它情况保留

bit[7] : Retimer EQ 扩展位, 此位只会在 16.0 GT/s 及更高速度下的Recovery.Equalization状态使用,在 8.0 GT/s 和其它状态为保留位

1b/1b编码

如果在发送TS1或者TS2时,需要调整DC Balance(直流平衡),未加扰的00或者FF

symbol0-6或者8-14的偶检验Byte

TS1 Symbol 8 – TS1标识符/EQ参数/同Symbol 0

TS1 Symbol 8

8b/10b编码

当链路速度为 2.5 或 5.0 GT/s 时,为 TS1 的标志,固定编码为 D10.2 (4Ah)

128b/130b编码

当链路速度在 8.0 GT/s 及以上时

bit[5:0] : 当 Symbol 6 的 EC 域为 01b 时,此位为 LF,其它情况代表当前链路速度对应的 Cursor 系数

bit[7:6] : 保留

1b/1b编码

同Symbol 0

TS1 Symbol 9 – TS1标识符/EQ参数/同Symbol 1

TS1 Symbol 9

8b/10b编码

当链路速度为 2.5 或 5.0 GT/s 时,为 TS1 的标志,固定编码为 D10.2 (4Ah)

128b/130b编码

当链路速度在 8.0 GT/s 及以上时

bit[5:0] : 当前链路速度对应的 Post-cursor 系数

bit[6] : 拒绝系数值位,此位只会在 LTSSM 中的Recovery.Equalization下的一些特定阶段置 1, 在 LTSSM 的其它状态,必须设置为 0

bit[7] : 奇偶校验(P), 此位为 Symbol 6,7,8 和 Symbol 9 的 bit[6:0] 的奇偶校验位,接收机必须根据接受到的 TS1 来计算此位,并将其与接收的奇偶校验位进行比较。只有计算出的奇偶校验位与此位一致时,接收到 TS1 才是有效的。

1b/1b编码

同Symbol 1

TS1 Symbol 10-13 – TS1标识符/同Symbol 2-5

TS1 Symbol 10-13

8b/10b编码

当链路速度为 2.5 或 5.0 GT/s 时,为 TS1 的标志,固定编码为 D10.2 (4Ah)

128b/130b编码

当链路速度为 8.0 GT/s 及以上时,为 TS1 的标志,固定编码为 (4Ah)

1b/1b编码

Symbol 10-13分别同Symbol 2-5

TS1 Symbol 14-15 – TS1标识符/同Symbol 6-7

TS1 Symbol 14-15

8b/10b编码

当链路速度为 2.5 或 5.0 GT/s 时,为 TS1 的标志,固定编码为 D10.2 (4Ah)

128b/130b编码

当链路速度为 8.0 GT/s 及以上时,可以是 TS1 的标志,固定编码为 (4Ah),需要加扰

也可以是用来维持直流平衡 (根据前面 Symbol 中 0 和 1 的个数来设置此位),绕过加扰

1b/1b编码

Symbol 14-15分别同Symbol 6-7

120b/130b symbol 14-15作用和取值依据:发射机每发送完一个TS1或者TS2之后,就会评估running DC Balance。根据评估后的running DC Balance来决定下一个TS中Sybmol 14和Symbol 15的取值。running DC Balance就是差分线上(经过了加扰和预编)逻辑电平1和逻辑电平0的个数差值,每条lane需要单独追踪running DC Balance,且每个方向可以追钟最多511比特的差异,即如果1比0多511个或者1比0少511个时,是可以正确的记录下来。最多能记录的0,1个数差异为511,如果检测到1比0多513个,running DC Balance也只会是511,如果下一次更新running DC Balance时,1比0少了两个,则running DC Balance变为509。running DC Balance在退出EI或者在数据流中后发送EIEOS时,会清零。在发送完Symbol 11之后,

如果running DC Balance > 31,则根据比特流中需要减少0的个数还是1的个数决定symbol 14和symbol 15的值,如果需要减少0的个数,则symbol 14和15固定为F7h,如果需要减少1的个数,则symbol 14固定为20h,symbol 15固定为08h

如果running DC Balance > 15,symbol 14固定为TS的标识符,如果需要减少0的个数,symbol 15固定为F7h,如果需要减少1的个数,symbol 15固定为08h

running DC Balance < 15,symbol 14和symbol 15为TS的标识符

Q:此处running DC Balance能达到511吗

A:正常情况下应该会比较困难,因为running DC Balance计算的来源是加扰后的值,本身其出现长0或者长1的概率就比较低,当出现0和1个数差别比较大时,又通过symbol 14-15补偿回来了。而且EIEOS会每隔32个TS就发送一次,就又会重新初始化LSFR,此时running DC Balance又重置为0,所以基本上只要前面32个TS中,不会出现running DC Balance不为0的情况,就基本不会出现running DC Balance到511的情况。

TS2OS每个符号作用

符号

gen1/2

gen3/4/5

gen6

0

TS2标识符(COM)

TS2标识符(2Dh)

TS2标识符(39h)

1

链路号

链路号

Link Number/EQ Byte0

2

lane号

lane号

Lane Number/EQ Byte1

3

N_FTS

N_FTS

EQ Byte2

4

速度标识

速度标识

EQ Byte3

5

链路控制

链路控制

速度标识

6

标准TS2OS/EQ TS2OS

EQ相关

链路控制

7

TS2标识符(D5.2,45h)

标准TS2OS或128b/130b EQ TS2OS

DC Balance/奇偶检验

8-13

TS2标识符(D5.2,45h)

TS2标识符(45)

Symbol 8-13分别同Symbol 0-5

14-15

TS2标识符(D5.2,45h)

TS2标识符(45)/直流平衡

Symbol 14-15分别同Symbol 6-7

TS2 Symbol 0

8b/10b编码

当链路速度为 2.5 或 5.0 GT/s 时,为 COM (K28.5)用于符号对齐

128b/130b编码

当链路速度为 8.0 GT/s 时,固定编码为 2Dh (8’b0010_1101)

1b/1b编码

39h

TS2 Symbol 1 – Link Number/EQ Byte0

TS2 Symbol 1

8b/10b编码

port 不支持 8.0 GT/s 及以上时,取值为 0-255 或者 PAD

128b/130b编码

支持 8.0 GT/s 及以上的 Downstream port 时,取值为 0-31 或者 PAD

1b/1b编码

表示为Link Number ,需要加扰,只有在Configuration,hot reset和Recovery.RcvrCfg时才表示为Link Number,取值为0-31和PAD(F7h)。接收机在Recovery.Idle时,只会检查这个symbol是否为PAD

在Recovery时表示EQ Byte 0,需要加扰,在其他状态保留

TS2 Symbol 2 – Lane Number/EQ Byte1

TS2 Symbol 2

8b/10b编码

当链路速度在 2.5 或者 5.0 GT/s 时,取值为 0-31 或者 PAD (K23.7)

128b/130b编码

当链路速度在 8.0 GT/s 或者更高时,取值为 0-31 或者 PAD (F7h)

1b/1b编码

在Configuration和Hot Reset时表示为Lane number,需要加扰Recovery.Idle时只会检查该symbol是否为PAD

在Recovery和Loopback.Entry表示为EQ Byte 1,需要加扰,其它状态保留0 |Recovery使用,在Loopback.Entry保留)Recovery中使用,在Loopback.Entry保留)

TS2 Symbol 3 – N_FTS/EQ Byte2

TS2 Symbol 3

8b/10b编码和128b/130b编码

N_FTS, 接收机需要的 Fast Training Sequences (简称 FTS)数量,取值 0-255

1b/1b编码

保留

TS2 Symbol 4 – 速度标识/EQ Byte3

TS2 Symbol 4

8b/10b编码和128b/130b编码

数据指示标志

bit[0] : 是否支持Flit Mode。0b为不支持Flit Mode, 1为支持Flit Mode

Bits [5:1] 支持的链路速度Detect状态进入Configuration.Complete协商成Flit模式后可以使用Polling状态以来,组件在Polling和Configuration状态传输的TS1中Supported Links Speeds为1 1111b,那么支持2.5,5.0,8.0,16.0,32.0和64.0GT/s + 其余保留

bit[6] : Autonomous Change/Selectable De-emphasis/Link Upconfigure Capalibity/L0p Capability TS2 中此位比 TS1 中的 Symbol 4 bit[6] 的功能要多

bit[7] : speed_change/SRIS Clocking,Configuration状态时,如果LinkUp=0b,此位为1表明链路就会工作在SRIS时钟模式下,如果此位为0表明链路会工作在common Clocking或者SRNS时钟模式。Downstream Port使用此位来确定Retimer(s)的时钟类型,LinkUp为1时在Configuration状态保留。在Recovery.RcvrCfg状态表示为speed_change,其它状态保留。Recovery.RcvrLock状态置1, 其它状态保留

1b/1b编码

保留

TS2 Symbol 5

8b/10b编码和128b/130b编码

链路控制 Deassert 可以理解为不执行相应动作,Assert 可以理解为执行相应动作,比如 bit[0] 当 Assert 后,会进入到 Hot Reset

bit[0] : Hot Reset 位

bit[1] : Disable Link 位

bit[2] : Loopback 位

bit[3] : 禁止加扰位 (适用于 2.5 和 5.0 GT/s)

bit[4] : Retimer Present bit (只对 2.5 GT/s 适用,其它速度保留)此位与 TS1 中的定义不同

bit[5] : Two Retimes Present,是否存在2个retimer

bit[7:6] : 增强链路行为控制bit[7:6] 只会在 32.0 GT/s 及更高速度, LinkUp = 0 且 LTSSM 处于Polling或者Configuration状态是才会被定义

1b/1b编码

保留

TS2 Symbol 6 – Standard TS2/EQ TS2/链路控制

TS2 Symbol 6

8b/10b编码

当链路速度在 2.5 或者 5.0 GT/s 时

如果是标准的 TS2, 编码为 D5.2 (45h),作为 TS2 的标识符

如果是 EQ TS2

128b/130b编码

当链路速度在 8.0 GT/s 或者更高与 TS1 不同

bit[3:0] : 保留

bit[5:4] : EQ 请求速度这些位只会在 LTSSM 中的Recovery.RcvfCfg状态使用,其它情况保留

bit[6] : Quisce Guarantee,此位只会在 LTSSM 中的Recovery.RcvfCfg状态使用,在 LTSSM 的其它状态保留

bit[7] : 请求 EQ, 此位只会在 LTSSM 中的Recovery.RcvrCfg状态使用,在 LTSSM 的其它状态保留

1b/1b编码

链路控制,在Recovery.RcvrCfg,Disable,Hot Reset或者Loopback状态使用,需要加扰,在Configuration状态保留

bit[3:0]

bit[7:4] : 保留

TS2 Symbol 7 – TS2标识符/standard TS2/ 128b/130b TS2/DC Balance/奇偶校验

TS2 Symbol 7

8b/10b编码

与 TS1 Symbol 7 定义不同

128b/130b编码

当链路速度在 8.0 GT/s 及以上时

如果是标准的 TS2, 为 TS2 的标志,固定编码为 45h

128b/130b EQ TS2 OS 只有在传输预设值且 LTSSM 处于Recovery.RcvrCfg时才有效

1b/1b编码

如果在发送TS1或者TS2时,需要调整DC Balance(直流平衡),未加扰的00或者FF

symbol0-6或者8-14的偶检验Byte

TS2 Symbol 8-13 – TS2标识符/同symbol 0-5

TS2 Symbol 8-13

8b/10b编码

2.5 或者 5.0 GT/s 时,TS2 的标志,固定为 D5.2 (45h)

128b/130b编码

8.0 GT/s 或者更高时,TS2 的标志,固定为 45h

1b/1b编码

同Symbol 0-5

TS2 Symbol 14-15 – TS2标识符/直流平衡/同Symbol 6-7

TS2 Symbol 14-15

8b/10b编码

2.5 或者 5.0 GT/s 时,TS2 的标志,固定为 D5.2 (45h)

128b/130b编码

8.0 GT/s 及更高时, 可以是 TS2 的标志 (编码为 45h),也可以用来维持直流平衡,取值规则同TS1

1b/1b编码

同Symbol 6-7

前一个TS和后一个TS可以被SKP打断,即SKP不影响连续TS的判断

8b/10b编码时,必须满足所有

TS1/2中Symbol 6跟前一个TS1/2 Symbol 6相匹配

128b/130b编码时,必须满足所有

TS1/2中的Symbol 6-9跟前一个Symbol的6-9匹配

保留位的选择

发射机必须发送0

接受机不会根据保留位来决定接受的TS是否有效

如果parity计算需要用到保留位,接收机计算parity时必须使用到保留位

接收机在确定是否连续时,TODO

接收机禁止使用保留位来实现某些功能性操作

8b/10b编码时,必须满足所有

Modified TS中的所有symbol跟前一个Modifed TS1/2对应的Symbol相同

Sybmol 15中的parity跟期望的一致,

链路上的所有lane传输的symbol 8-14必须一致

SKPOS (Skip Ordered Set)用于链路两端不同不同频率的补偿, 物理层接受机中逻辑子层的弹性缓冲 (elastic buffer)用于实现补偿

接收机评估 SKPOS 并在内部添加或者移除 SKP 符号,以防止 elastic buffer 上溢或者下溢。

SKPOS分为Standard SKPOS和Control SKPOS, Control SKPOS的最后四个符号跟Standard SKPOS不同,Control SKPOS包括了奇偶校验位和数据的奇偶校验位

发射机发送的SKPOS长度是固定 的,gen1/2 4symbol, gen3/4/5 16个symbol,gen6是40个symbol

接收端可以根据两端频率不同增加或删除SKP符号

1b/1b编码下没有Standard SKPOS,即64.0GT/s无Standard SKPOS

Standard SKPOS和Control SKPOS(Y:yes,支持,N:no,不支持)

速度

支持Standard SKPOS(Non-Flit)

支持Control SKPOS(Non-Flit)

支持Standard SKPOS(Flit)

支持Control SKPOS(Flit)

2.5GT/s

Y

N

Y

N

5.0GT/s

Y

N

Y

N

8.0GT/s

Y

N

Y

Y

16.0GT/s

Y

Y

Y

Y

32.0GT/s

Y

Y

Y

Y

64.0GT/s

N

Y

N

Y

发射机不同速度下发送的Standard SKPOS组成

symbol

2.5GT/s,5.0GT/s

8.0GT/s,16.0GT/s

32.0GT/s

64.0GT/s

0

COM(K28.5),BCh

AAh

99h

无

1-3

SKP(K28.0),1Ch

AAh

99h

无

4-11

无

AAh

99h

无

12

无

E1h

E1h

无

13

无

00-FFh

00-FFh

无

14

无

00-FFh

00-FFh

无

15

无

00-FFh

00-FFh

无

8b/10b编码下的SKPOS

symbol 0 : COM符号

symboo 1-3 : SKP符号

128b/130b编码下的Standard SKPOS

Symbol 0 – (4*N -1), N可以是 1 到 5 (对于发射机方向而言, N = 4, 因为发射机发的 SKPOS 是 16 个 symbol)

对于 8.0 GT/s 和 16.0 GT/s, 为 AAh, 对于 32.0 GT/s 已经更高速度为 99h, 这些 Symbol 为 SKP 符号, Symbol 0 为 SKPOS 的标识符

Symbol 4*N

E1h (SKP_END 符号), 标识SKPOS在三个符号后结束

Symbol 4*N + 1

00-FFh, 如果 LTSSM 在 Polling.Compliance, 为 AAh; 如果先前的一个 block 是 Data Block (数据快),bit[7] 为 数据奇偶校验位, bit[6:0] 为 LFSR[22:16], 否则 bit[7] = ~LFSR[22], bit[6:0] = LFSR[22:16]

Symbol 4*N + 2

00-FFh, 如果 LTSSM 处于 Polling.Compliance, 为 Error_Status[7:0], 否者为 LFSR[15:8]

Symbol 4*N + 3

00-FFh, 如果 LTSSM 处于 Polling.Compliance, 为 ~Error_Status[7:0], 否则为 LFSR[7:0]

发射机不同速度下发送的Control SKPOS组成

symbol

2.5GT/s,5.0GT/s

8.0GT/s,16.0GT/s

32.0GT/s

0-11

无

AAh

99h

12

无

E1h

E1h

13

无

00-FFh

00-FFh

14

无

00-FFh

00-FFh

15

无

00-FFh

00-FFh

128b/130b编码下的Control SKPOS

Symbol 0 – (4*N -1), N可以是 1 到 5

对于 8.0 GT/s 和 16.0 GT/s, 为 AAh, 对于 32.0 GT/s 及以上, 为 32.0 GT/s, 这些 symbol 为 SKP Symbol, Symbol 0 是 SKPOS 的标识符

Symbol 4*N

78h, SKP_END_CTL Symbol, 标识在三个或者更多个 Symbol 之后, Control SKPOS 的结束

Symbol 4*N + 1

bit[7] : 数据奇偶校验位 (Data Parity)

bit[6] : 第一个 Retimer 的数据奇偶校验位

bit[5] : 第一个 Retimer 的奇偶校验位

bit[4:0] : Margin CRC[4:0]

Symbol 4*N + 2

bit[7] : Margin Parity (奇偶校验)

bit[6:0] : 与 Usage Model 的值有关

Symbol 4*N + 3

bit[7:0] : 与 Usage Model 的值有关

1b/1b编码发送的Control SKPOS组成

symbol

64.0GT/s

0,4, 8,12,16,20

F0h

1,5, 9,13,17,21

0Fh

2,6,10,14,18,22

F0h

3,7,11,15,19,23

0Fh

24,28

FFh

25,29

F0h

26,30

00h

27,31

F0h

32-39

F0h或Phy Payload[7:0]/[15:8]…[63:56]

1b/1b编码下的Control SKPOS

symbol 32-39:如果正在传输TS0OS,则为F0h,否则位Phy Padload对应比特

接收到的SKPOS可以是24,32,40,48或者56

SKPOS是由SKPs(F00F_F00F)跟着SKP_END(FFF0_00F0)加PHY Payload(8B)构成

8b/10b下的接收机接收的SKPOS为一个COM字符加1-5个SKP(最多增加或删除2个SKP符号)

接收端128b/130b编码下的SKPOS可以是8(删除了8个SKP符号,N=1),12(删了4个SKP符号,N=2),16(SKP符号无增减,N=3),20(增加4个SKP符号,N=4),24(增加8个SKP符号,N=5)

对于Standard SKPOS和Control SKPOS,接收端都是一样的规则

时钟补偿,通过增删SKP来补偿链路两端比特率差别(在物理层逻辑子层中的elastic中执行)

在数据流中

当需要发送SKPOS时,所有lane都需要发送相同格式的SKPOS(标准SKPOS或者Control SKPOS)

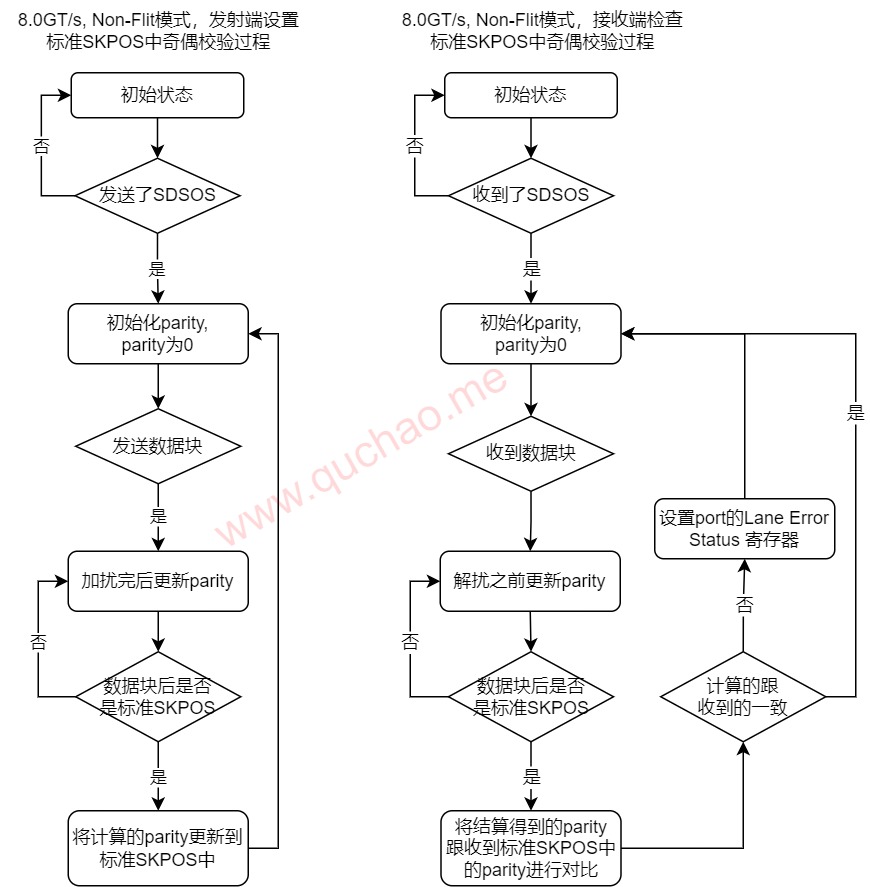

Non-Flit模式,速度在8.0GT/s时,标准SKPOS中data parity的规则

标准SKPOS中的奇偶校验为偶校验,校验针对某条lane上的所有数据块,不同lane之间奇偶检验位是独立的

DSP和USP发射机计算标准SKPOS中奇偶校验位的规则

当有SDSOS需要发送时,初始化奇偶校验(计算出来的奇偶校验为0,SDSOS前面没有数据)

在加扰执行过后,更新奇偶校验位(需要使用到数据块载荷的每一比特)

数据块后跟着标准SKPOS,则标准SKPOS中的奇偶校验为当前奇偶校验(把计算出来的奇偶校验更新到标准SKPOS中去,奇偶校验不针对SKPOS)

在发送标准SKPOS后,初始化奇偶校验位

DSP和USP接收机计算标准SKPOS中奇偶校验位的规则

在数据接绕前更新奇偶校验

当数据块后跟着标准SKPOS,每条lane单独比较收到的奇偶校验和计算出来的奇偶校验,如果不一致,就接收机必须设置Port’s Lane Error Status寄存器,不匹配不能算成Receiver Error,所以不会导致链路重新训练

当收到标准SKPOS之后,初始化奇偶校验

8.0GT/s,Non-Flit模式下,收发端对标准SKPOS中parity的处理如下图所示

Non-Flit模式,速度在8.0/16.0/32.0GT/s时或者Flit模式下,速度在8.0/16.0/32.0GT/s时,标准SKPOS或者control SKPOS中data parity的规则

DSP和USP发射机计算parity的规则

当LTSSM处于Recovery.Speed时,初始化Parity

当发送SDSOS时,初始化parity

在数据块加扰执行后,更新parity. (在Flit模式下,parity在FEC后计算)

数据块后跟着标准SKPOS时,将计算出来的parity更新到标准SKPOS中

Control SKPOS中的Data Parity,First Retimer Data Parity和Second Retimer Data Parity都设置成当前计算出来的parity

在发送完Control SKPOS后,初始化Parity。但是在发送完标准SKPOS后不会初始化Parity

DSP和USP接收机处理parity的规则

当LTSSM进入Recovery.Speed时,初始化Parity

当收到SDSOS时,初始化Parity

收到数据后,在解扰前,根据数据块的每一个比特更新parity(Flit模式,parity计算在FEC前)

当收到Control SKPOS后,每条lane都要用计算出来的parity跟收到的data parity进行比较.如果不一致,接收机必须设置Local Data Parity Mismatch Status寄存器对应的比特.建议只在数据流后跟着Control SKPOS才检查. parity不匹配不是接收机错误,所以不会让链路重新训练。

当收到Control SKPOS后,每条lane都用计算出来的parity跟收到的First Retimer Data Parity进行比较,如果不一致,需要记录在First Retimer Data Parity Mismatch Status寄存器中,推荐数据后跟着Control SKPOS才进行检查,不一致不会接收机错误不会导致链路重新训练

当收到Control SKPOS后,每条lane都用计算出来的parity和收到的second retimer data parity对比,不一致需要记录在Second Retimer Data Parity Mismatch Status寄存器中,推荐数据后跟着Control SKPOS才进行检查,不一致不会接收机错误不会导致链路重新训练

当收到一个标准SKPOS后,也允许用计算出来的parity跟收到的data parity比特进行比较,但是,如果比较出来不一样,并不会影响Lane Error Status寄存器

当收到Control SKPOS后会初始化Parity,但是收到标准SKPOS时不会初始化parity

1b/1b下,data parity的计算规则

DSP和USP发射机计算parity规则

当LTSSM处于Recovery.Speed时,初始化parity

当发送SDSOS时,初始化parity

当发送SKPOS(Control SKPOS)后,初始化parity

在加扰执行后,更新parity,所以格雷码编码和预编码不影响parity计算

数据块后跟着Control SKPOS,data parity为当前计算出来的parity

Control SKPOS中data parity,First Retimer Data Parity和Second Retimer Data Parity都设置为当前计算出来的parity

DSP和USP接收机处理parity的行为

当LTSSM处于Recovery.Speed时,初始化parity

当收到SDSOS时,初始化parity

当收到Control SKPOS后,每条lane都要用计算出来的parity跟收到的data parity进行比较.如果不一致,接收机必须设置Local Data Parity Mismatch Status寄存器对应的比特.建议只在数据流后跟着Control SKPOS才检查. parity不匹配不是接收机错误,所以不会让链路重新训练。

当收到Control SKPOS后,每条lane都用计算出来的parity跟收到的First Retimer Data Parity进行比较,如果不一致,需要记录在First Retimer Data Parity Mismatch Status寄存器中,推荐数据后跟着Control SKPOS才进行检查,不一致不会接收机错误不会导致链路重新训练

当收到Control SKPOS后,每条lane都用计算出来的parity和收到的second retimer data parity对比,不一致需要记录在Second Retimer Data Parity Mismatch Status寄存器中,推荐数据后跟着Control SKPOS才进行检查,不一致不会接收机错误不会导致链路重新训练

当收到Control SKPOS后,初始化parity

发射机通用规则

多lane的link上,所有lane发送的symbol都是相同的频率。即不同lane上的比特率差异为0ppm。

发送SKPOS时,在多lane的link上,所有lane都必须同时发送相同长度和类型(Standard或者Control)的SKPOS,但是在Loopback.Actvie时,Loopback Follower可以不遵守该条规则(因为Loopback Follower环回数据时会增加或者删除SKPOS)

接收机通用规则

non flit 模式下数据流中SKPOS插入间隔

编码

条件

间隔

8b/10b

1. 非SRIS

1180-1538个symbol Times

8b/10b

1.SRIS

小于154个Symbol Times

128b/130b

1.非SRIS

370 – 375个block,一个block为130比特

128b/130b

1. SRIS

小于38个Blocks

Flit模式下数据流中SKPOS插入间隔

2.5GT/s和5.0GT/s时,1180-1538个symbol插入一个SKPOS,插入SKPOS的时机是在Flit边界

8.0GT/s以上数据流中SKPOS插入间隔,以Flit个数 计算

8.0GT/s以上数据流中SKPOS插入间隔

链路宽度和时钟模式

x16

x8

x4

x2

x1

1b/1b,common clock或者SRNS

748

374

187

93

46

128b/130b,common clock

374

187

93

46

23

1b/1b,SRIS

74

37

18

9

4

SRIS,128b/130b

37

18

9

4

2

希望进入低功率链路状态的发射机在停止传输之前发送此信息。收到后,接收者就知道要为低功率状态做好准备。接收器检测到此有序集并通过忽略输入错误直到退出电气空闲来准备链接进入电气空闲。 发送EIOS 后不久,发射机将其差分电压降低到小于 20mV 峰值

在发射机进入 Electrical Idle (简称 EI ) 前,如果没有特别说明,发射机必须发送 Electrical Idle Ordered Set Sequence (简称EIOSQ )。在 2.5 GT/s, 8.0 GT/s, 16.0 GT/s 和 32.0 GT/s 时,EIOSQ 为一个 Electrical Idle Ordered Set (简称 EIOS ),在 5.0 GT/s 为两个 EIOS。EIOS 在不同速度下其内容不完全一样。

不同速度下的 EIOS 组成

symbol

2.5GT/s,5.0GT/s

8.0GT/s,16.0GT/s,32.0GT/s

64.0GT/s

0

COM(K28.5,BCh)

66h

0Fh

1

IDL(K28.3,7Ch)

66h

F0h

2

IDL(K28.3,7Ch)

66h

0Fh

3

IDL(K28.3,7Ch)

66h

F0h

4,6,8,10,12,14

无

66h

0Fh

5,7,9,11,13,15

无

66h

F0h

让本端TX进入EI

告知对端本端TX已经入EI

编码

发送端要求

8b/10b

发射机必须 发送COM+3个IDL symbol

128b/130b

发射机必须 发送EIOS的Symbol 0到13,但是可以在symbol 14或者15终止(既不要求发送symol 14或者15)

1b/1b

满足其一 ,认为收到了EIOS:

接受端规则

EIOS的所有symbol都不需要加扰

Non-Flit模式下

128b/130b编码,EDS Token后必须跟SKP,EIOS或者EIEOS

128b/130b编码,在当前数据块的最后一个DW,发送EDS Token,紧接着下一个block是EIOS或者EIEOS,如果是EIOS,则LTSSM需要进入低功耗管理状态;不是进入低功耗状态,则发送EIEOS

在合适的block边界应该收到EIEOS,SKPOS或者EIOS的任意一种

接收机收到SKP或者在数据流中收到EIOS,该EIOS的作用是进入L0p,该情况下不会使得LFSR移位

Flit模式结束数据流不会发送EDS,数据流可以被EIOS(优先级高于进入低功耗状态,如L1)或者EIEOS(在进入Recovery时)打断

连续收到EIEOS+EIOS或者EIEOS+SKPOS的组合是Framing Error

128b/130b下,loopback lead发送OS块,OS块的第一个Symbol跟SKPOS,EIOS或者EIEOS相匹配,剩下的OS必须是一个完整有效的SKPOS,EIOS或者EIEOS

Electrical Idle Exit Ordered Sets (简称EIEOS ) 是用来退出 EI 状态, EIEOS 在不同速度下也有不同的格式。

EIEOS序列 (Electrical Idle Exit Ordered Set Sequence,简称EIEOSQ ) 在 5.0 GT/s, 8.0 GT/s, 16.0 GT/s 由一个 EIEOS 构成,在 32.0 GT/s 时由 2 个连续的 EIEOS 构成

不同速度下的 EIEOS 组成

symbol

2.5GT/s

5.0GT/s

8.0GT/s

16.0GT/s

32.0GT/s

64.0GT/s

0

无

COM(K28.5,BCh)

00h

00h

00h

00h

1

无

EIE(K28.7,FCh)

ffh

00h

00h

00h

2

无

EIE(K28.7,FCh)

00h

ffh

00h

00h

3

无

EIE(K28.7,FCh)

ffh

ffh

00h

00h

4

无

EIE(K28.7,FCh)

00h

00h

ffh

00h

5

无

EIE(K28.7,FCh)

ffh

00h

ffh

00h

6

无

EIE(K28.7,FCh)

00h

ffh

ffh

00h

7

无

EIE(K28.7,FCh)

ffh

ffh

ffh

00h

8

无

EIE(K28.7,FCh)

00h

00h

00h

ffh

9

无

EIE(K28.7,FCh)

ffh

00h

00h

ffh

10

无

EIE(K28.7,FCh)

00h

ffh

00h

ffh

11

无

EIE(K28.7,FCh)

ffh

ffh

00h

ffh

12

无

EIE(K28.7,FCh)

00h

00h

ffh

ffh

13

无

EIE(K28.7,FCh)

ffh

00h

ffh

ffh

14

无

EIE(K28.7,FCh)

00h

ffh

ffh

ffh

15

无

D10.2

ffh

ffh

ffh

ffh

EIEOS 为 Gen2 增加的内容,在 2.5 GT/s 链路速度下不存在

确保电路能够退出 EI 状态,使用的低频序列

128b/130b 编码时用来做块对齐 (Block Alignment)

8b/10b编码,且链路速度为 5.0 GT/s 时

进入 Configuration.Linkwidth.Start 状态后,发送第一个 TS1OS 前,必须发送 EIEOS

进入 Recovery.RcvrLock 状态后,发送第一个 TS1OS 前,必须发送 EIEOS

在 LTSSM 中的 Configuration.Linkwidth.Start, Recovery.RcvrLock 和 Recovery.RcvrCfg 状态,每发送 32 个 TS1/2 后要发送一个 EIEOS。TS1/2 的数量会被清零,当满足下面的条件时 :

发送了一个 EIEOS

当在 Recovery.RcvrCfg 状态时,收到第一个 TS2OS

128b/130b 编码,EIEOS 需要满足的规则

进入 Configuration.Linkwidth.Start 状态后,发送第一个 TS1OS 前,必须发送 EIEOS

进入 Recovery.RcvrLock 状态后,发送第一个 TS1OS 前,必须发送 EIEOS

当数据流 (Data Stream) 结束且没有发送 EIOS, 也没有进入 LTSSM 中的 Recovery.RcvrLock 状态时,在 EDS Framing Token 后面接 EIEOS

在需要传输 TS1/2 的状态,每32个 TS1/2 传输后必须跟 EIEOS。当满足下面条件时, TS1/2 的数量会被清零

传输了一个 EIEOS

在 Recovery.RcvrCfg 状态,收到第一个 TS2OS 后

在 Configuration.Complete 状态,收到第一个 TS2OS 后

Downstream Port 在 LTSSM 中 Recovery.Equalization 的 Phase 2 并且任意一条 lane 收到 2 个连续的 TS1 (Reset EIEOS Interval Count 必须要为1,Symbol 6 bit[2])

Upstream port 在 LTSSM 中 Recovery.Equalization 的 phase 3并且收到 2 个连续的 TS1 (Reset EIEOS Interval Count 必须要为1,Symbol 6 bit[2])

LTSSM 中的 Recovery.Equalization 状态每传输 65536 个 TS1 后 (Reset EIEOS Interval Count 位要设置为 1)

Fast Training Sequence (简称FTS) 用于从 L0s 向 L0 跳转时实现位锁定 (bit lock)和符号锁定(Symbol lock)。

接收机使用 FTS 检测是否退出 EI 状态并且让接受输入数据的电路实现位锁定和符号锁定。

1b/1b编码无FTS,因为FTS是用在L0s到L0转变,1b/1b编码下无L0s状态,即64.0GT/s无FTS

最大允许请求的 FTSs 数量 (The maximum number of FTSs,简称 N_FTS) 为 255,最大的 bit lock 时间为 4*255*10 UI

传FTS前,需要先传EIEOS(Electrical Idle Exit OS,gen2及以上)

不同速度下的 FTSOS 组成

符号

2.5GT/s,5.0GT/s

8.0GT/s,16.0GT/s,32.0GT/s

64.0GT/s

0

COM(K28.5,BCh)

55h

无

1

k28.1,3Ch

47h

无

2

K28.1,3Ch

4Eh

无

3

K28.1,3Ch

C7h

无

4

无

CCh

无

5

无

C6h

无

6

无

C9h

无

7

无

25h

无

8

无

6Eh

无

9

无

ECh

无

10

无

88h

无

11

无

7Fh

无

12

无

80h

无

13

无

8Dh

无

14

无

8Bh

无

15

无

8Eh

无

SDSOS (The Start of Data Stream) 表示从有序集块(Ordered Set)到数据流(Data Stream)的转换, 只在128b/130b 编码下使用, 并且只会在 LTSSM 中的 Configuration.Idle、Recovery.Idle 和 Tx_L0s.FTS 中会使用到,SDSOS 后面跟数据流

在 8b/10b 下没有, 即 2.5 GT/s 和 5.0 GT/s 不存在 SDSOS

不同速度下的 SDSOS 组成

符号

2.5GT/s,5.0GT/s

8.0GT/s,16.0GT/s

32.0GT/s

64.0GT/s

0

无

E1h

E1h

B1h

1-3

无

55h

87h

C6h

4

无

55h

87h

B1h

5-7

无

55h

87h

C6h

8

无

55h

87h

B1h

9-11

无

55h

87h

C6h

12

无

55h

87h

B1h

13-15

无

55h

87h

C6h

55h = 01010101b, 87h = 10001110b, C6h = 11000110 在更高的速度下,识别低频的01跳变可能更容易

SDSOS只在Configuration.Idle,Recovery.Idle和Tx_L0s.FTS以及Loopback状态发送,因为只有在这些状态下才会发送开始准备发送数据

在非Loopback时,Non-Flit模式下,SDSOS后面必须跟着数据块,数据块的第一个symbol也是数据流的第一个symbol

在1b/1b编码下,当满足发送SDSOS时,发射机必须发送2个背靠背的SDSOS.

1b/1b编码下,SDSOS必须必须对齐到128b(16B)的边界

Flit模式,编码为128b/130b或1b/1b编码时,SDSOS发送完后必须发送Control SKPOS,Control SKPOS后面跟着数据流的第一个symbol

SDSOSQ (SDSOS Sequence,SDSOS序列)在128b/130b下指一个SDSOS,在1b/1b编码下指2个背靠背的SDSOS在1b/1b编码下,如果收到4(1b/1b编码下SDSDOSQ有8个,2*4)个好的B1_C6_C6_C6(4B),其中至少有两个位于偶数4字节对齐位置(如Bytes 0-3,8-11),则认为收到的SDSOSQ有效

打赏支持

很好的文章

@cszdzc 哈哈,谢谢,后面还得完善一下,目前主要是还是协议直译,加点自己的理解

gen6的TS1、TS2和gen3-5的格式不一样

@cszdzc 感谢纠正,后面会修改

应该是在Filt模式下,SDS OS发送完成后吧

@assa 嗯,对了一下6.2的协议,你是对的,已经修改