recovery.eq

Equalization 介绍

EQ是equalization的简写,EQ(均衡)的作用是调节每条lane上发射机和接收机电压,使得收发双方能更精确的识别数据,EQ只在Gen3及以上才有。在2.5GT/s和5.0GT/s时只有de-emphasis,固定为-3.5dB或者-6.0dB。链路的EQ过程就是在调整发射机和接收机的设置使得信号的质量更好,发射机和接收机的调整是针对lane的,即每条lane上发射机和接收机的设置可以不一样,与当前LTSSM关联的每一条lane都必须参与到EQ过程。

EQ 原理

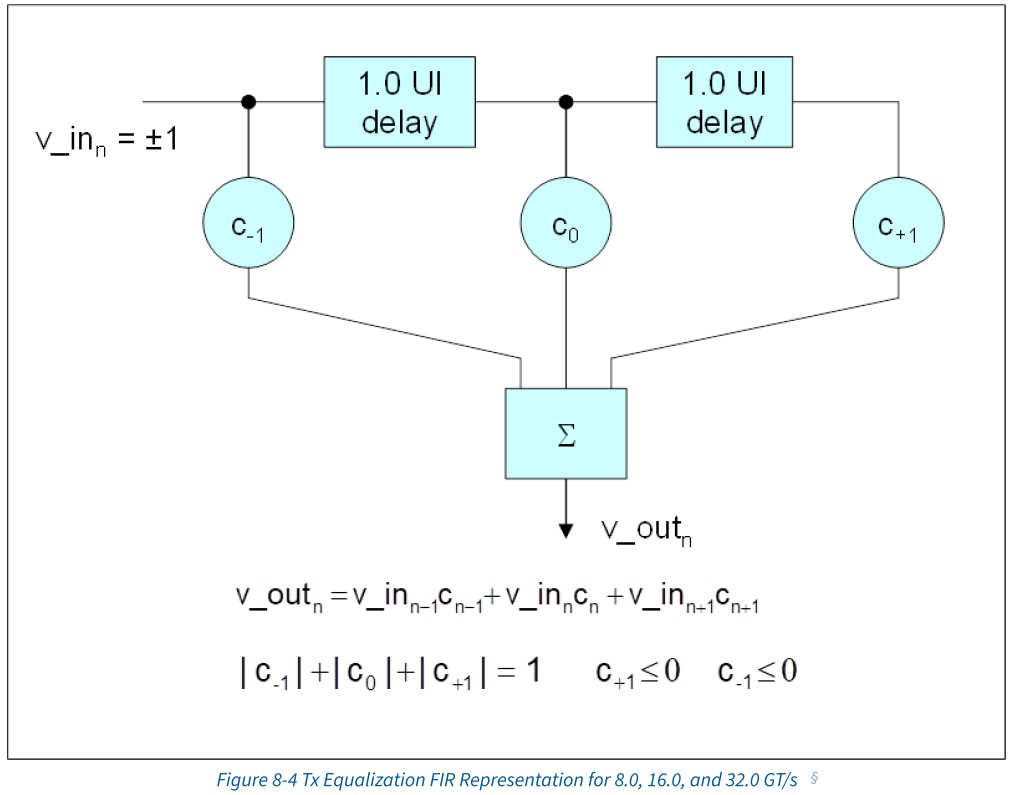

Gen3/4/5采用3阶抽头的FIR,其输出电压跟输入电压之间的关系如下图

有三个系数C-1(pre-cursor),C0(cursor coefficient)和C+1(post-cursor),其中只有两个是独立的,调节系数可以调节Tx的发送电压。

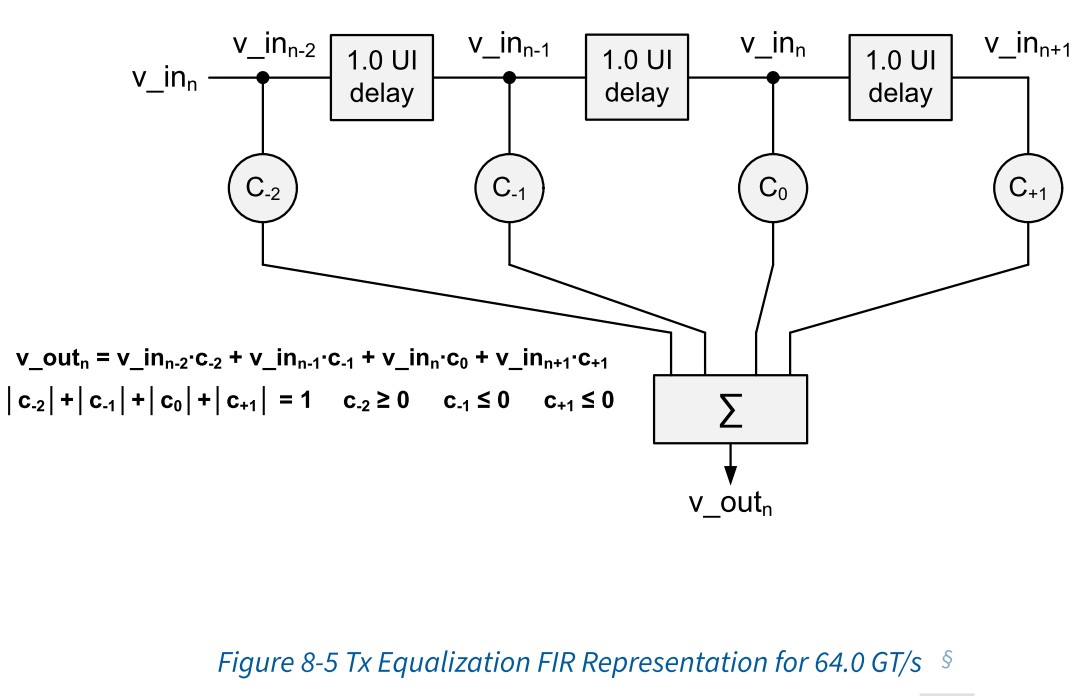

Gen6采用的4阶抽头的FIR,增加了一个参数C-2(2nd pre-cursor),其输出电压和输入电压之间的关系如下图:

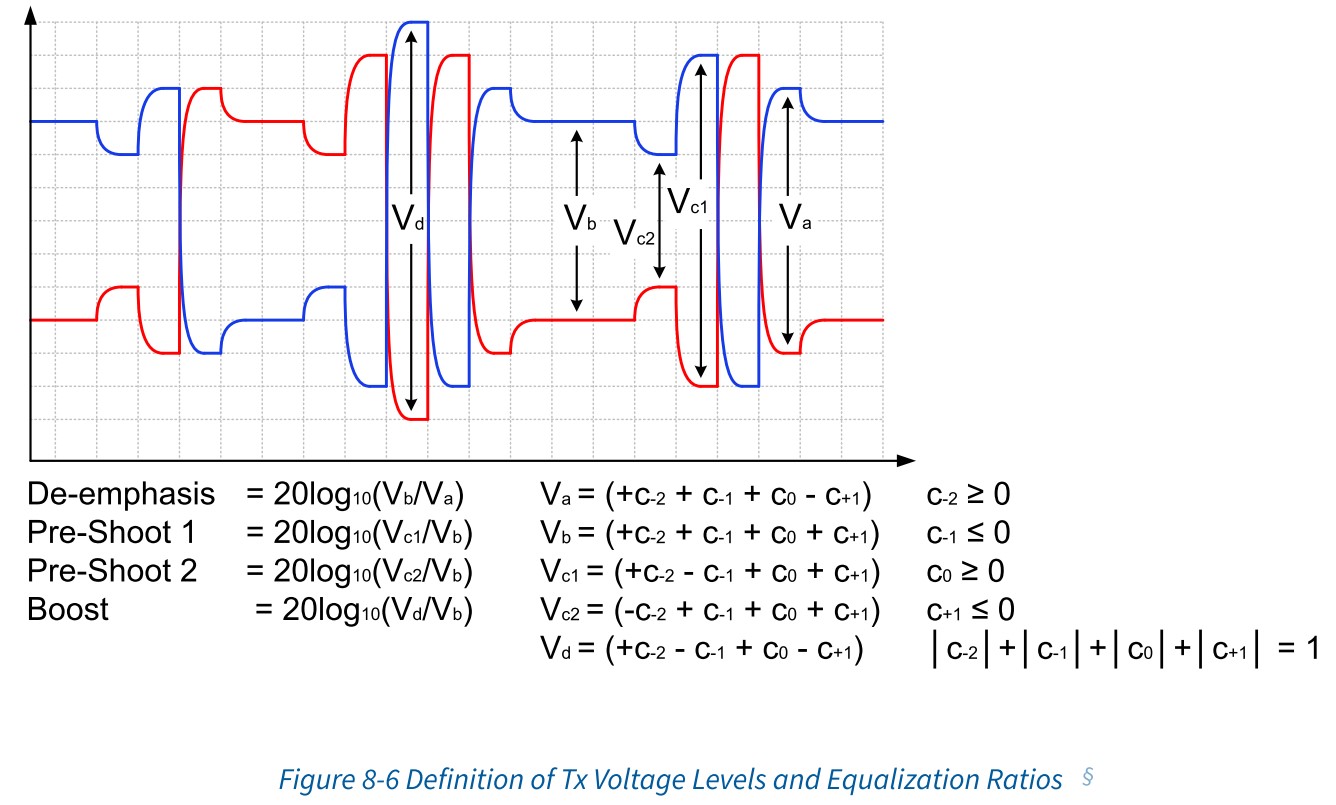

不同的C-1,C0和C+1的组合产生了四种电压值:maximum-height(Vd), normal(Va), de-emphasized(Vb)和pre-shoot(Vc),这些系数也会体现在TS1中。

preshoot, 在当前时间提高电压来改善信号质量,Gen1/2 比较简单,Gen1 只有-3.5db的de-emphsis,Gen2 有-3.5db或者-6db的de-emphsis。de-emphasis电压在Gen3有了更多的选择

根据系数绝对值的和定义了FS(Full Swing; FS=|C-2|+|C-1|+|C0|+|C-1|),FS在phas 1状态建议给对方,FS的范围如下:

- FS 如果在24到63之间,则是full swing mode

- FS 如果在12到63之间,则是reduced swing mode

- 当链路速率小于64.0GT/s,C-2 固定位0

发送机在Phase 1状态建议自己的LF(Low Frequency)值,这对应于发射机可以产生的最小差分电压,即LF/FS乘以发射机的最大差分电压。

这些系数之间存在下列的关系

- |C-1| <= Floor(FS/4) ,floor 取整

- |C-2|+|C-1|+|C0|+|C-1| = FS 不允许峰值功率随适应而变化

- C0 – | C-1| + | C-2|-|C+1| >= LF

- |C-2| <= Floor (FS/8)

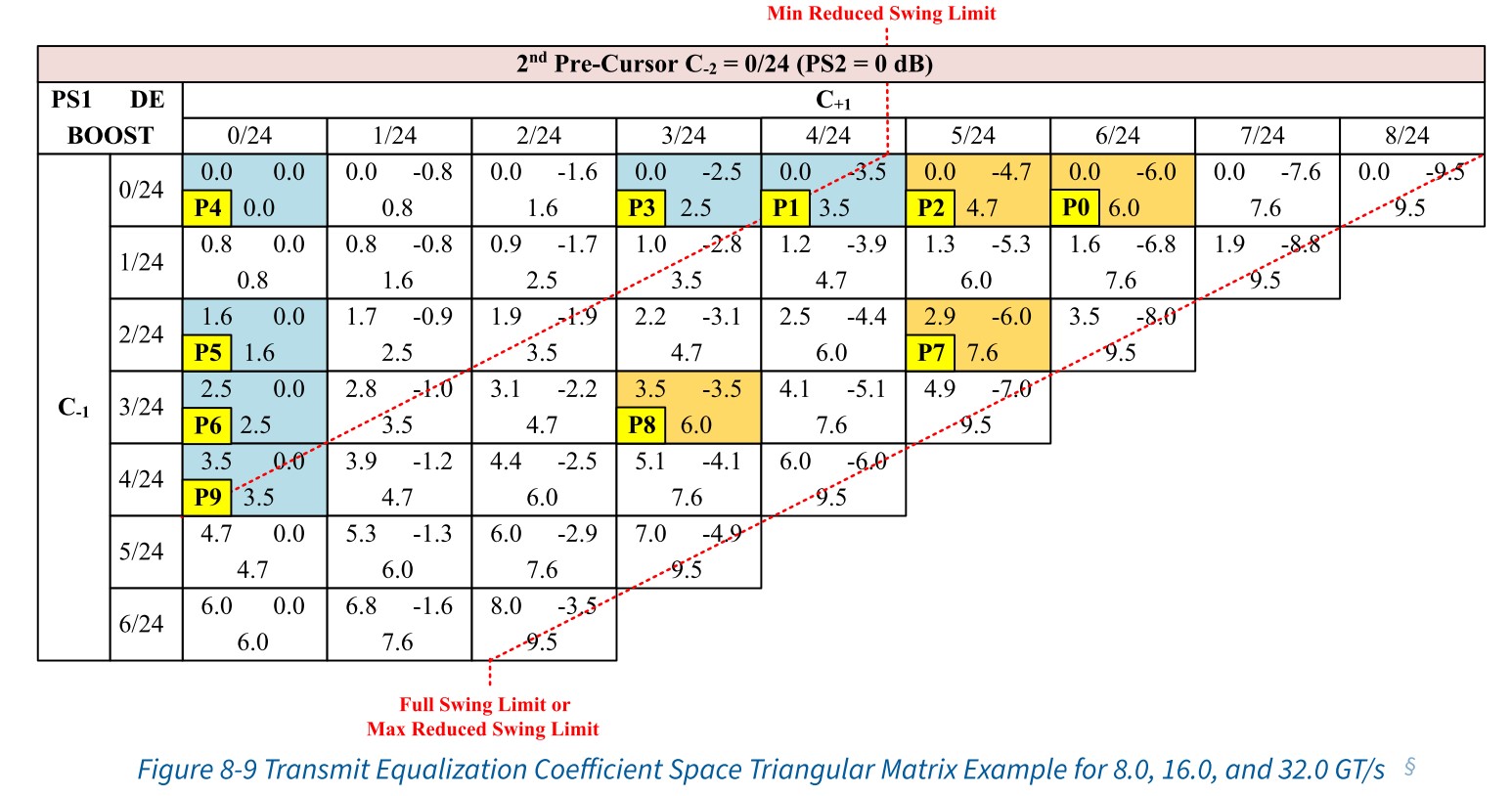

在最初切换到8.0GT/s时,使用11种预设中的一种来调节Tx的发射电压(在发EQ TS1/TS2中包含了preset), 如果使用预设的值,错误率小于10^-12,不需要进一步调节Tx的发射电压,如果不满足错误率的要求, 会进行细调,直接调节C-1和C+1, 进而调节Tx的发射电压。

当工作在在8.0GT/s,16.0GT/s和32.0GT/s时,TX必须支持下面11组预设的presets值(其中P10与FS和LF有关),表格如下:

| Preset# | Preshoot 2(dB) | Preshoot 1(dB) | De-emphasis(dB) | C-2 | C-1 | C+1 | Va/Vd | Vb/Vd | Vc1/Vd | Vc2/Vd |

|---|---|---|---|---|---|---|---|---|---|---|

| P4 | 0.0 | 0.0 ± 1 dB | 0.0 ± 1 dB | 0.000 | 0.000 | 0.000 | 1.000 | 1.000 | 1.000 | 1.000 |

| P1 | 0.0 | 0.0 ± 1 dB | -3.5 ± 1 dB | 0.000 | 0.000 | -0.167 | 1.000 | 0.666 | 0.666 | 0.666 |

| P0 | 0.0 | 0.0 ± 1 dB | -6.0 ± 1 dB | 0.000 | 0.000 | -0.250 | 1.000 | 0.500 | 0.500 | 0.500 |

| P9 | 0.0 | 3.5 ± 1 dB | 0.0 ± 1 dB | 0.000 | -0.167 | 0.0000 | 0.666 | 0.666 | 1.000 | 0.666 |

| P8 | 0.0 | 3.5 ± 1 dB | -3.5 ± 1 dB | 0.000 | -0.125 | -0.125 | 0.750 | 0.500 | 0.750 | 0.500 |

| P7 | 0.0 | 3.5 ± 1 dB | -6.0 ± 1 dB | 0.000 | -0.100 | -0.200 | 0.800 | 0.400 | 0.600 | 0.400 |

| P5 | 0.0 | 1.9 ± 1 dB | 0.0 ± 1 dB | 0.000 | -0.100 | 0.000 | 0.800 | 0.800 | 1.000 | 0.800 |

| P6 | 0.0 | 2.5 ± 1 dB | 0.0 ± 1 dB | 0.000 | -0.125 | 0.000 | 0.750 | 0.750 | 1.000 | 0.750 |

| P3 | 0.0 | 0.0 ± 1 dB | -2.5 ± 1 dB | 0.000 | 0.000 | -0.125 | 1.000 | 0.750 | 0.750 | 0.750 |

| P2 | 0.0 | 0.0 ± 1 dB | -4.4 ± 1 dB | 0.000 | 0.000 | -0.200 | 1.000 | 0.600 | 0.600 | 0.600 |

| p10 | 0.0 | 0.0 ± 1 dB | Note2 | 0.000 | 0.000 | Note 2 | 1.000 | Note 2 | Note 2 | Note 2 |

Note 2 : P10 boost limits不是固定的,因为

当上面11组参数也无法达到要求时,可以进行细调节,直接调节C-1和C+1的值。可以调节的范围如下(从这个图也可以发现,preset就是几组特殊的组合):

当工作在64.0GT/s时,TX必须完全支持下列所有的presets(粗调)

| Preset # | Preshoot 2 (dB) | Preshoot 1 (dB) | De-emphasis (dB) | c-2 | c-1 | c+1 | Va/Vd | Vb/Vd | Vc1/Vd | Vc2/Vd |

|---|---|---|---|---|---|---|---|---|---|---|

| Q0 | 0.0 ±0.5 dB | 0.0 ±0.5 dB | 0.0 ±0.5 dB | 0.000 | 0.000 | 0.000 | 1.000 | 1.000 | 1.000 | 1.000 |

| Q1 | 0.0 ±0.5 dB | 1.6 ±0.5 dB | 0.0 ±0.5 dB | 0.000 | -0.083 | 0.000 | 0.834 | 0.834 | 1.000 | 0.834 |

| Q3 | 0.0 ±0.5 dB | 0.0 ±0.5 dB | -1.6 ±0.5 dB | 0.000 | 0.000 | -0.083 | 1.000 | 0.834 | 0.834 | 0.834 |

| Q4 | 0.0 ±0.5 dB | 0.0 ±0.5 dB | -3.5 ±0.5 dB | 0.000 | 0.000 | -0.167 | 1.000 | 0.666 | 0.666 | 0.666 |

| Q5 | -1.3 ±0.5 dB | 4.7 ±1.0 dB | 0.0 ±0.5 dB | 0.042 | -0.208 | 0.000 | 0.584 | 0.584 | 1.000 | 0.500 |

| Q6 | -1.6 ±0.5 dB | 3.5 ±0.5 dB | -3.5 ±0.5 dB | 0.042 | -0.125 | -0.125 | 0.750 | 0.500 | 0.750 | 0.416 |

| Q7 | -2.9 ±0.5 dB | 4.7 ±1.0 dB | 0.0 ±0.5 dB | 0.083 | -0.208 | 0.000 | 0.584 | 0.584 | 1.000 | 0.418 |

| Q8 | -3.5 ±0.5 dB | 6.0 ±1.0 dB | 0.0 ±0.5 dB | 0.083 | -0.250 | 0.000 | 0.500 | 0.500 | 1.000 | 0.334 |

| Q9 | -4.4 ±1.0 dB | 6.9 ±1.0 dB | -1.6 ±0.5 dB | 0.083 | -0.250 | -0.042 | 0.500 | 0.416 | 0.916 | 0.250 |

| Q10 | 0.0 ±0.5 dB | 0.0 ±0.5 dB | Note 2 | 0.000 | 0.000 | Note 2 | 1.000 | Note 2 | Note 2 | Note 2 |

Note 2 :

EQ过程有四个阶段,phase0,phase1,phase2,phase3。

EQ几种模式:Full EQ, eq bypass to high, no need eq

EQ 规定

如果是第一次进入8.0GT/s以及更高速率时,必须执行EQ过程,除非是链路双方都支持no EQ过程并在链路训练过程中建议no EQ过程。当变量LinkUp为1时,组件的发射器设置必须达到适合所有操作条件和数据速率,组件不得要求以任何数据速率重复均衡过程以获得可靠的操作,尽管有重复该过程的规定。

TX EQ Preset设置

EQ 状态机

EQ phase 0

Upstream Lanes EQ Phase 0

只有Upstream Lane才有EQ Phase 0,USP在进入Recovery.Equalization时就是EQ Phase0。USP在 EQ phase0会将start_equalization_w_preset 设置为0,并根据速度的不同清掉不同的变量和寄存器

- 当前工作速度是8.0GT/s,设置如下的变量和寄存器:

- 变量 equalization_done_8GT_data_rate设置为1

- Link Status 2寄存器中的:

- Equalization 8.0 GT/s Phase 1 Successful

- Equalization 8.0 GT/s Phase 2 Successful

- Equalization 8.0 GT/s Phase 3 Successful

- Link Equalization Request 8.0 GT/s

- Equalization 8.0 GT/s Complete

- 当前工作速度是16.0GT/s时,设置如下的变量和寄存器:

- 变量 equalization_done_16GT_data_rate设置为1

- 16.0GT/s Status寄存器中的

- Equalization 16.0 GT/s Phase 1 Successful

- Equalization 16.0 GT/s Phase 2 Successful

- Equalization 16.0 GT/s Phase 3 Successful

- Link Equalization Request 16.0 GT/s

- Equalization 16.0 GT/s Complete

- 当前工作速度是32.0GT/s时,设置如下的变量和寄存器:

- 变量 equalization_done_32GT_data_rate设置为1

- 32.0 GT/s Status寄存器中的:

- Equalization 32.0 GT/s Phase 1 Successful

- Equalization 32.0 GT/s Phase 2 Successful

- Equalization 32.0 GT/s Phase 3 Successful

- Link Equalization Request 32.0 GT/s

- Equalization 32.0 GT/s Complete

- 当前工作速度是64.0GT/s时,设置如下的变量和寄存器:

- 变量 equalization_done_64GT_data_rate设置为1

- 64.0 GT/s Status寄存器中的:

- Equalization 64.0 GT/s Phase 1 Successful

- Equalization 64.0 GT/s Phase 2 Successful

- Equalization 64.0 GT/s Phase 3 Successful

- Link Equalization Request 64.0 GT/s

- Equalization 64.0 GT/s Complete

Upstream Lanes EQ Phase 0 发射机要求

如果Recovery.Equalization是从Loopback.Entry进入,发射机发送TS0OS/TS1OS,TS中的字段有如下要求:

- EC字段必须是00b

- 每条lane中的Transmitter Preset设置为需要使用的值

- 如果发送的TS1OS

- TS1OS中的Pre-cursor,Coefficient,Curosr Coefficient和Post-cursor Coefficient字段的值需要跟Transmitter Preset字段对应对应的上。

- 如果设备发送的EQ TS1OS需要LTSSM直接从

Configuration.Linkwidth.Start跳转到Loopback.Entry,则发射机的preset值必须使用EQ TS1OS的Preset字段。 - 如果设备发送的标准TS1OS需要LTSSM直接从

Configuration.Linkwidth.Start跳转到Loopback.Entry,则发射机的preset值必须依赖于具体实现

在EQ phase0,根据速度的不同,发射机发射本段不同的发射机参数,通过TS1OS告诉DSP。

- 如果工作速度是在8.0GT/s

- TS1OS中的 preset 来源于最从一次从2.5GT/s或者5.0GT/s过渡到8.0GT/s时收到的EQ TS2OS中的Transmitter Preset字段

- 如果工作速度时在16.0GT/s

- TS1OS中的 preset来源于最近一次从8.0GTs/过渡到16.0GT/s时收到的128b/130b EQ TS2OS中的Transmitter Preset字段

- 如果工作速度是在32.0GT/s 且变量perform_equalization_for_loopback是0

- TS1OS中的preset来源于最近从某个速度过渡到32.0GT/s时收到的TS2OS中的Transmitter Preset字段。

- 如果是协商成了bypass EQ,则最近收到的TS2OS是EQ TS2,如果32.0GT/s是从8.0GT/s或者16.0GT/s过渡而来,则最近收到的TS2是128b/130b EQ TS2OS

- 如果工作速度是在64.0GT/s且变量perform_equalization_for_loopback是0

- TS1OS中的preset来源于最近从某个速度过渡到64.0GT/s时收到的TS2OS中的Transmitter Preset

- 如果协商成了bypass EQ,则最近收到的TS2OS 是EQ TS2,如果64.0GT/s是从16.0GT/s或者32.0GT/s直接升上来,则最近收到的TS2OS为128b/130b EQ TS2OS

Upstream Lanes EQ Phase0 LTSSM

| 状态跳转(优先级从上到下) | 跳转条件 |

|---|---|

Recovery.EQ.Phase0 -> Recovery.EQ.phase1 |

满足其一: 1.所有配置过的lane收到2个连续的TS1OS,其中EC为01b 2. 所有配置过的lane收到2个连续的TS0OS,其中EC为01b且Retimer Equalization Extend比特为0 |

Recovery.EQ.phase0 -> Loopback.Entry |

perform_equalazation_for_loopback是1且12ms超时 |

Recovery.EQ.phase0 -> Recovery.Speed |

12ms超时 |

当跳转到Recovery.EQ.phase1后:

- 接收机必须完成比特锁定,并在在接受pin上收到第一个有效OS的第一个有效比特后,必须在2ms之内识别OS

- 接受到两个连续TS0/TS1OS中的LF和FS值必须存储下来,如果Upstream Port想要调节Downstream Port的系数,则该系数会在Phase 2使用。所以Phase2是Upstream Port调节Downstream Port的TX

当跳转到Recovery.Speed后:

- 变量successful_speed_negotiation设置为0

- 如果速率是8.0GT/s时,Link Status 2寄存器的Equalization 8.0GT/s Complete比特设置为1

- 如果速率是16.0GT/s时,16.0GT/s Status寄存器的Equalization 16.0GT/s Complete比特设置为1

- 如果速率是32.0GT/s时,32.0GT/s Status寄存器的Equalization 32.0GT/s Complete比特设置为1

- 如果速率是64.0GT/s时,64.0GT/s Status寄存器的Equalization 64.0GT/s Complete比特设置为1

EQ phase 1

Downstream Lanes EQ Phase1

- DSP进入

Recovery.Equalization时,状态为phase1 - 把变量 start_equalization_w_preset 清零。

- Link Status 3 寄存器中下列值清零:

- Perform Equalization

当链路速率在 8.0 GT/s时:

- Link Status 2 寄存器中下列值清零:

- Equalization 8.0 GT/s Phase1 Successful

- Equalization 8.0 GT/s Phase2 Successful

- Equalization 8.0 GT/s Phase3 Successful

- Link Equalization Request 8.0 GT/s

- Equalization 8.0 GT/s Complete

- 变量equalization_done_8GT_data_rate 设置为1,1代表没有完成?

当链路速率在 16.0 GT/s时:

- 16.0 GT/s Status 寄存器中下列值清零:

- Equalization 16.0 GT/s Phase1 Successful

- Equalization 16.0 GT/s Phase2 Successful

- Equalization 16.0 GT/s Phase3 Successful

- Link Equalization Request 16.0 GT/s

- Equalization 16.0 GT/s Complete

- 变量equalization_done_16GT_data_rate 设置为1

当链路速率在 32.0 GT/s 时

- 32.0 GT/s Status 寄存器中下列值清零:

- Equalization 32.0 GT/s Phase1 Successful

- Equalization 32.0 GT/s Phase2 Successful

- Equalization 32.0 GT/s Phase3 Successful

- Link Equalization 32.0 GT/s Request

- Equalization 32.0 GT/s Complete

- 变量equalization_done_32GT_data_rate 设置为1

Downstream Lane EQ Phase1发射机要求:

发射机发送TS0OS/TS1OS,TS0OS/TS1OS中的一些字段要求如下:

- Transmitter preset针对当前速度

- EC 为 01b,如果是TS0OS,EC字段最开始00b,直到2个收到2个连续的TS0OS,且Retimer Equalization Extend比特为0,EC字段为01b的TS0OS后,才将EC字段更改为01b

- 每条 Lane 上的 Transmitter Preset(symbol 6 bit[6:3])设置为当前速率下对应的Transmitter Preset设置

- FS,LF字段设置为适当的值

- 如果需要发送TS1OS,Post-cursor系数字段需要设置为对应某条lane的Transmitter Preset.

- 每一条配置过的lane的Transmitter Preset设置必须遵守如下规则(越靠前优先级越高):

- 从

Loopback.Entry进入Recovery.Equalization时

- 从

Configuration.Linkwidth.Start进入Loopback.Entry时,如果发送的如果是 EQ TS1,发射机的预设值必须使用lane under test指定的EQ TS1OS中的Preset字段 - 从

Configuration.Linkwidth.Start进入Loopback.Entry时,如果发送的是标准的TS1OS,Transmitter Preset值基于具体实现,但必须是支持的值 - 如果perform_equalization_for_loopback_64GT是1,Loopback Follower必须在发送的TS0OS/TS1OS中建议64.0GT/s support为1(比如设置速度标识符必须要是Flit模式编码)

- 如果在最近一次经过

Recovery.RcvrCfg时,收到了8个连续的128b/130b EQ TS2OS,其中Transmitter Preset值是支持的且当前速度在16.0GT/s或者更高,则必须使用128b/130b EQ TS2OS中的Transmitter Preset值 - 如果在最近一次经过

Recovery.RcvrCfg时,收到了8个连续的EQ TS2OS,其中Transmitter Preset是支持的,当前速度是32.0GT/s,且执行了EQ bypass to 32.0GT/s,则必须使用EQ TS2OS中的Transmitter Preset值 - 否则,Transmitter Preset由寄存器指定,前提是寄存器的Transmitter Preset编码是支持到的值,并且是非保留的值。当工作在8.0GT/s时,由Lane Equalization Control寄存器得Downstream port 8.0GT/s Transmitter Prest字段决定;当工作在16.0GT/s时,由16.0GT/s Lane Equalization Control寄存器得Downstream Port 16.0GT/s Transmitter Preset字段决定;当工作在32.0GT/s时,由32.0GT/s Lane Equalization Control寄存器得Downstream Port 32.0GT/s Transmitter Preset字段决定;当工作64.0GT/s时,由64.0GT/s Lane Equalization Control寄存器得Downstream Port 64.0GT/s Transmitter Preset字段决定;

- 否则就使用自定义的方法选择一个支持的Transmitter Preset值。

- 从

Downstream Port在进入Phase 1之后,允许等待长达500ns在评估收到的TS0OS/TS1OS中的信息,原因是接受端逻辑需要时间稳定。

** 从 Configuration.Linkwidth.Start 进入 Loopback.Entry时,如果发送的时标准的 TS1,

‘’‘SDS作用, 为何sync header不能作为data stream的开始’‘’

Downstream Lane EQ phase1 LTSSM

状态跳转有优先级

DSP从Recovery.EQ.Phase1往下一个状态跳转时没有出现不同优先级同时往一个状态跳转,如果变量perform_equalization_for_loopback是1且PCI Express Capabilities寄存器中的Flit Mode Supported域是1b时,Phase 2和Phase 3必须执行。

| 状态跳转(优先级从上到下) | 跳转条件 |

|---|---|

Recovery.EQ.Phase1 -> Recovery.EQ.Phase2 |

满足所有 1.所有配置过的lane收到2个连续的TS0OS/TS1OS(其中EC为01b) 2. DSP想执行Phase 2和Phase 3 |

Recovery.EQ.Phase1 -> Recovery.RcvrLock |

满足所有 1. 所有配置的lane都收到2个连续的TS0OS/TS1OS(其中EC=01b), 2. 变量perform_equalization_for_loopback为0 3. DSP不想执行Phase 2和Phase 3 |

Recovery.EQ.Phase1 -> Loopback.Entry |

24ms超时且变量perform_equalization_for_loopback是1 |

Recovery.EQ.Phase1 -> Recovery.Speed |

24ms超时且变量perform_equalization_for_loopback是0 |

当跳转到Recovery.EQ.Phase2后:

- 接收机必须完成比特锁定,然后在接受pin上收到第一笔有效的OS之后,必须在2ms之内识别到Ordered Sets.

- 如果速度是8.0GT/s,则Link Status 2寄存器的Equalization 8.0GT/s Phase 1 Successful比特需要置1

- 如果速度是16.0GT/s,则16.0GT/s Status 寄存器的Equalization 16.0GT/s Phase 1 Successful 比特需要置1

- 如果速度是32.0GT/s且变量perform_equalization_for_loopback是0,则32.0GT/s Status寄存器的Equalization 32.0GT/s Phase 1 Successful比特需要置1

- 如果速度是64.0GT/s且变量perform_equalization_for_loopback是0,则64.0GT/s Status寄存器的Equalization 64.0GT/s Phase 1 Successful比特需要置1

- 如果DSP想要调节USP的Transmitter coefficients,则必须存储收到的连续2个TS0OS/TS1OS中的LF和FS值,方便在Phase 3使用。因此Phase 3是DSP调节USP的TX

当跳转到Recovery.RcvrLock后:

- 如果工作速度是8.0GT/s,需要把Link Status 2寄存器中的Equalization 8.0GT/s Phase 1 Successful, Equalization 8.0GT/s Phase 2 Successful, Equalization 8.0GT/s Phase 3 Successful 和 Equalization 8.0GT/s Complete比特置为1

- 如果工作速度是16.0GT/s,需要把16.0 Status寄存器中的Equalization 16.0GT/s Phase 1 Successful, Equalization 16.0GT/s Phase 2 Successful, Equalization 16.0GT/s Phase 3 Successful 和 Equalization 16.0GT/s Complete比特置为1

- 如果工作速度是32.0GT/s,需要把32.0 Status寄存器中的Equalization 32.0GT/s Phase 1 Successful, Equalization 32.0GT/s Phase 2 Successful, Equalization 32.0GT/s Phase 3 Successful 和 Equalization 32.0GT/s Complete比特置为1

- 如果工作速度是64.0GT/s,需要把64.0 Status寄存器中的Equalization 64.0GT/s Phase 1 Successful, Equalization 64.0GT/s Phase 2 Successful, Equalization 64.0GT/s Phase 3 Successful 和 Equalization 64.0GT/s Complete比特置为1

- 如果当前工作速度是64.0GT/s,发射机在跳转到

Recovery.RcvrLock之前,必须发送24个TS0OS,其中EC为00b。 - 跳转到

Recovery.RcvrLock的原因是DSP基于平台和电气属性决定不执行Phase 2和Phase 3

当跳转到Recovery.Speed后:

- successful_speed_negotiation设置为0

- 如果速度是8.0GT/s,设置Link Status 2寄存器中的Equalization 8.0GT/s Complete比特位为1

- 如果速度是16.0GT/s,设置16.0 GT/s Status寄存器中的Equalization 16.0GT/s Complete比特位为1

- 如果速度是32.0GT/s,设置32.0 GT/s Status寄存器中的Equalization 32.0GT/s Complete比特位为1

- 如果速度是64.0GT/s,设置64.0 GT/s Status寄存器中的Equalization 64.0GT/s Complete比特位为1

Upstream Lanes EQ Phase1发射机要求

发射机发送TS0OS/TS1OS,其中Transmitter setting在Phase 0 决定好了。EC字段设置为01b,FS、LF和Post-curosr系数字段设置为每条lane对应的发射机设置。如果Recovery.Equalization是从Loopback.Entry进入且变量perform_equalization_for_loopback_64GT是1,Loopback Follower必须在发送的TS0OS/TS1OS中建议支持64.0GT/s(比如速度表示必须使用Flit模式编码)

Upstream Lanes EQ Phase1 LTSSM

状态跳转有优先级

| 状态跳转(优先级从上到下) | 跳转条件 |

|---|---|

Recovery.EQ.Phase1 -> Recovery.EQ.Phase2 |

所有配置过的lane都收到2个连续的TS0OS/TS1OS,其中EC为10b |

Recovery.EQ.Phase1 -> Loopback.Entry |

变量perform_equalization_for_loopback为1且12ms超时 |

Recovery.EQ.Phase1 -> Recovery.RcvrLock |

变量perform_equalization_for_loopback为0且所有配置过的lane收到8个连续的TS0OS/TS1OS,其中EC为00b |

Recovery.EQ.Phase1 -> Recovery.Speed |

变量perform_equalization_for_loopback为0且12ms超时 |

当跳转到Recovery.EQ.phase2后:

- 如果速度是8.0GT/s,则把Link Status 2寄存器中的Equalization 8.0GT/s Phase 1 Successful 域置1

- 如果速度是16.0GT/s,则把16.0 GT/s Status寄存器中的Equalization 16.0GT/s Phase 1 Successful 域置1

- 如果速度是32.0GT/s且变量perform_equalization_for_loopbck为0,则把32.0 GT/s Status寄存器中的Equalization 32.0GT/s Phase 1 Successful 域置1

- 如果速度是64.0GT/s且变量perform_equalization_for_loopbck为0,则把64.0 GT/s Status寄存器中的Equalization 64.0GT/s Phase 1 Successful 域置1

当跳转到Recovery.RcvrLock后:

- 如果速度是8.0GT/s,则把Link Status 2寄存器中的Equalization 8.0GT/s Phase 1 Successful 和Equalization 8.0 GT/s Complete域置1

- 如果速度是16.0GT/s,则把16.0 GT/s Status寄存器中的Equalization 16.0GT/s Phase 1 Successful 和Equalization 16.0GT/s Complete域置1

- 如果速度是32.0GT/s,则把32.0 GT/s Status寄存器中的Equalization 32.0GT/s Phase 1 Successful 和Equalization 32.0GT/s Complete域置1

- 如果速度是64.0GT/s,则把64.0 GT/s Status寄存器中的Equalization 64.0GT/s Phase 1 Successful 和Equalization 64.0GT/s Complete域置1

当跳转到Recovery.Speed后:

- 变量successful_speed_negotiation设置为0

- 如果速度是8.0GT/s,则把Link Status 2寄存器中的Equalization 8.0 GT/s Complete域置1

- 如果速度是16.0GT/s,则把16.0 GT/s Status寄存器中的Equalization 16.0GT/s Complete域置1

- 如果速度是32.0GT/s,则把32.0 GT/s Status寄存器中的Equalization 32.0GT/s Complete域置1

- 如果速度是64.0GT/s,则把64.0 GT/s Status寄存器中的Equalization 64.0GT/s Complete域置1

EQ phase 2

Downstream Lane EQ phase 2

发送的内容和速度之间的关系

| 速度 | 发送的内容 | 条件 |

|---|---|---|

| 64.0GT/s | TS0OS(EC为10b) | 进入该状态时,不是所有的lane都收到了2个连续的TS0OS(EC要为10b) |

| 64.0GT/s | TS1OS(EC为10b) | 进入该状态时,所有的lane都收到了2个连续的TS0OS(EC为10b) |

| 2.5-32.0GT/s | TS1OS(EC为10b,每条lane独立的coefficient设置) | gen5及以下 |

TS1OS里面cofficient或者preset的设置规则以及发射机的行为:

- 简单而言就是来自于接收到的TS1OS

- 进入phase 2时,收到了2个连续的TS0OS/TS1OS(其EC=10b)或者收到的连个连续的TS0OS/TS1OS(需要EC为10b)中的preset或者coefficients值跟前面接收到的两个连续的TS0OS/TS1OS(需要EC为10b)中的不一样,那么DSP需要更新其TX发出去的TS1OS中对应的字段。

- 如果最近收到的2个连续的TS1OS的preset或者coefficients是合法并且本段支持((的,则需要更新本段发送出去的TS1OS,由此可以看出,EQ Phase2是USP来调整DSP的eq参数。DSP更新规则为:将发射机对应的pin脚的preset或者coefficients调整为要求的值,要求来源于接收机接收到的TS1OS。并且发射机对应的pin需要保持该preset或者coefficients一段时间,好让USP来评估当前preset或者coefficients的效果。DSP在接收端接收到请求新设置的第二个TS0OS/TS1OS的结束后500毫秒内,新设置在发送端仍然i有效。发射机参数的改变可能会导致非法的电压幅度或非法的电压参数,但是非法的电压幅度或者电压参数持续时间超过1ns。DSP发送出去的TS1OS中,发射机Preset对应比特设置为接收到的值(也是USP要求的值,如果是preset请求),Pre-cursor和Post-cursor Coefficients设置为发射机的设置(如果是preset或者coefficients请求),并且TS1OS中的Reject Coefficient值需要被清掉。

- 如果最近收到的2个连续的TS1OS中的preset或者coefficients是非法或者本段不支持,发射机不会改变发射机已经使用的设置,但是需要将这个消息告知给USP,通知的方法就是将发射出去的TS1OS中的Reject Coefficient值设置为1。

Downstream Lane EQ phase2 状态跳转

| 状态跳转(优先级从上到下) | 跳转条件 |

|---|---|

Recovery.EQ.Phase2 -> Recovery.EQ.Phase3 |

所有配置过的lane收到2个连续得TS0OS/TS1OS,其中EC为11b |

Recovery.EQ.Phase2 -> Loopback.Entry |

当前速度小于64.0GT/s,变量perform_equalization_for_loopback是1,且32ms超时,超时时间允许增加0到4ms |

Recovery.EQ.Phase2 -> Loopback.Entry |

当前速度等于64.0GT/s,变量perform_equalization_for_loopback是1,且64ms超时,超时时间允许增加0到4ms |

Recovery.EQ.Phase2 -> Recovery.Speed |

当前速度小于64.0GT/s,32ms超时,超时时间允许增加0到4ms(36ms) |

Recovery.EQ.Phase2 -> Recovery.Speed |

当速度等于64.0GT/s,64ms超时,允许超时时间增加0到4ms(70ms) |

当跳转到Recovery.EQ.Phase3后:

- 如果速度是8.0GT/s, Link Status 2寄存器中的Equalization 8.0GT/s Phase 2 Successful设置为1

- 如果速度是16.0GT/s, 16.0 GT/s Status 寄存器中的Equalization 16.0GT/s Phase 2 Successful 设置为1

- 如果速度是32.0GT/s且变量perform_equalizatoin_for_loopback是0,32.0 GT/s Status 寄存器中的Equalization 32.0GT/s Phase 2 Successful 设置为1

- 如果速度是64.0GT/s且变量perform_equalizatoin_for_loopback是0,64.0 GT/s Status 寄存器中的Equalization 64.0GT/s Phase 2 Successful 设置为1

当跳转到Recovery.Speed后:

- 变量successful_speed_negotiation设置为0

- 如果速度是8.0GT/s,Link Status 2寄存器中的Equalization 8.0GT/s Complete域设置为1b

- 如果速度是16.0GT/s,16.0 GT/s Status寄存器中的Equalization 16.0GT/s Complete域设置为1

- 如果速度是32.0GT/s,32.0GT/s Status寄存器中的Equalization 32.0GT/s Complete域设置为1

- 如果速度是64.0GT/s,64.0GT/s Status寄存器中的Equalization 64.0GT/s Complete域设置为1

Upstream Lane EQ phase 2

发射机在此状态发送TS0OS/TS1OS,其中EC为10b。port在此状态必须每条lane独立的评估并打到最优的设置,既EQ Phase是USP需要评估,那就是在调节DSP的TX,因此EQ phase是USP调节DSP的TX。当perform_equalization_for_loopback是1时,EQ过程必须只能在待测试的lane上进行。为了评估新的有效系数,有如下规则需要遵守:

- 通过设置Transmitter Preset比特到特定的值,并且将Use Preset比特设置为1来请求新的Preset值,USP通过TS1OS告知DSP。

- 通过设置TS1OS中的Pre-cursor,Cursor和Post-Cursor系数字段,并将Use Preset设置为0来请求新的Pre-cursor, cursor和Post-Cursor。

- 当发出一个请求后,必须持续该请求,直到1us或者该请求的评估完成,以耗时最后的为准。

- 如果接受DSP传输的请求设置,则必须等待一个时间(500ns加上往返延迟以及Upstream Port的逻辑延迟)

- 获得块对齐后需要评估收到的OS。在等待期间,Upstream Port可以简单的忽略它接受的一切,因为在转换到所要求的设置期间,比特流可能是无效的,因此要求在等待周期结束后,需要获得有效的块对齐。

- 如果在一个具体实现的时间后(加上上面所要求的等待时间)后不能获得块对齐,无论如何,建议继续对传入的比特流执行接收器评估。

- 如果收到2个连续的TS1OS中,Transmitter Preset比特(针对Preset请求)或者Pre-Cursor, cursor和Post-Curser系数字段(针对coefficients请求)跟要求的一致并且Reject Coefficient Values字段为0,则请求是被接受的,取决于接收机评估的结果,可以考虑作为最后设置的候选

- 如果收到2个连续的TS1OS中,Transmitter Preset比特(针对Preset请求)或者Pre-Cursor, cursor和Post-Curser系数字段(针对coefficients请求)跟要求的一致并且Reject Coefficient Values字段为1,那么该请求被DSP拒绝,并且禁止作为最后设置的候选

- 接收机在开始评估后,如果在一个基于具体实现的时间之后,没有收到2个连续的TS1OS,其中Transmitter Preset比特(针对Preset请求)或者Pre-Cursor, cursor和Post-Curser系数字段(针对coefficients请求)跟要求的一致,则该请求禁止作为最后设置的候选

- 根据评估标准和要求,Upstream Port负责设置它传输TS0OS/TS1OS中的Reset EIEOS Interval Count比特,禁止使用接受到TS1OS中的Use Preset比特来作为决定request是被接受或是被拒绝

- 在32.0GT/s以及更低的速率,从发送请求到完成评估,每个preset或coefficients请求所花费的总时间必须少于2毫秒。在优化的最后阶段需要更长的评估时间的实现可能会继续请求超过2 ms限制的相同设置,但必须遵守此阶段的超时(8.0,16.0和32.0GT/是24ms,在64.0GT/s是48ms)并且这个例外不能超过两次。如果请求者无法在超时期间内接收有序集,则可以假定所请求的设置在该Lane中不起作用。

- 在64.0GT/s或者更改的速度,允许设备在任意时间内评估每个预设或系数请求。必须谨慎地管理评估,以便能够成功地寻找可接受的预设或系数。在此阶段中花费的总时间必须仍然遵守超时。

- 所有新的预设或系数设置必须同时显示在所有已配置的lane上。任何给定lane如果不希望更改当时的设置,则允许其继续传输当前预设或系数作为其新值。

Upstream Lanes EQ Phase2 LTSSM

状态跳转有优先级

| 状态跳转(优先级从上到下) | 跳转条件 |

|---|---|

Recovery.EQ.Phase2 -> Recovery.EQ.Phase3 |

变量perform_equalization_for_loopback是1,lane under test工作在最优设置,且接收到的2个连续TS1OS中,Retiemr Equalization Extend比特位0 |

Recovery.EQ.Phase2 -> Recovery.EQ.Phase3 |

变量perform_equalization_for_loopback是0,所有配置过的lane都工作在它们的最优设置,并且工作速度在8.0GT/s或者所有lane都收到2个连续的TS1OS,其中retimer Equalization Extend比特是0 |

Recovery.EQ.Phase2 -> Loopback.Entry |

变量perform_equalization_for_loopback是1,当且速度小于64.0GT/s且24ms超时,超时时间允许增加0到2ms(26ms) |

Recovery.EQ.Phase2 -> Loopback.Entry |

变量perform_equalization_for_loopback是1,当速度是64.0gT/s且48ms超时,超时时间运训增加0到2ms(50ms) |

Recovery.EQ.Phase2 -> Recovery.Speed |

当前速度小于64.0GT/s且24ms超时,超时时间允许增加0到2ms |

Recovery.EQ.Phase2 -> Recovery.Speed |

当前速度是64.0GT/s且48ms超时,超时时间允许增加0到2ms |

当跳转到Recovery.EQ.Phase3之后:

- 如果工作速度在8.0GT/s,则Link Status 2寄存器中的Equalization 8.0GT/s Phase 2 Successful置为1

- 如果工作速度在16.0GT/s,则16.0GT/s Status 寄存器中的Equalization 16.0GT/s Phase 2 Successful置为1

- 如果工作速度在32.0GT/s,则32.0GT/s Status 寄存器中的Equalization 32.0GT/s Phase 2 Successful置为1

- 如果工作速度在64.0GT/s,则64.0GT/s Status 寄存器中的Equalization 64.0GT/s Phase 2 Successful置为1

当跳转到Recovery.Speed之后:

- 变量successful_speed_negotiation设置为0

- 如果工作速度是8.0GT/s,Link Status 2寄存器中的Equalization 8.0GT/s Complete设置为1

- 如果工作速度是16.0GT/s,16.0GT/s Status寄存器中的Equalization 16.0GT/s Complete设置为1

- 如果工作速度是32.0GT/s,32.0GT/s Status寄存器中的Equalization 32.0GT/s Complete设置为1

- 如果工作速度是64.0GT/s,64.0GT/s Status寄存器中的Equalization 64.0GT/s Complete设置为1

EQ phase 3

Downstream Lane EQ phase 3

在此状态,发射机发送EC=11b的TS1OS。Port必须每条lane相互独立的评估并达到最优的设置,因此在EQ phase3是DSP调节USP的TX。如果变量perform_equalization_for_loopback是1,EQ过程只在Lane Under Test(待测试的Lane)执行。为了评估新的preset或者coefficient设置是最优的,有如下规则需要遵守:

- 通过将Transmitter Preset比特设置为所需值并将Use Preset设置为1b来请求新的preset

- 通过将Pre-cursor, Cursor和 Post-Cursor Coefficient字段设置所需要的值并将Use Preset设置为0来请求新的Pre-cursor, Cursor 和 Post-Cursor Coefficients。

- 一旦发出了改请求,必须持续改请求至少1us或者评估改请求完成,持续时间以后完成的为准。

- 如果接受Upstream Port正在使用的请求设置,则需要等待一个时间(500ns加上往返延迟,包括通过下游端口的逻辑延迟)。然后获得块对齐,然后评估收到的OS。

- 在等待的时间中,Downstream Port可以简单的忽略掉它接收到的任何东西,因为在过渡到要求的设置中,收到的比特流可能是无效的。因此在等待的时间过后,需要获取块对齐。

- 如果在一个自定义规定的时间内没有获得块对齐(除了上述规定的时间外),无论如何,建议继续对传入的比特流执行接收器评估。

- 如果收到2个连续的TS1OS,其中Transmitter Preset(对于Preset请求)或者Pre-cursor, Cursor或者Post-Cursor Coefficient(对于coefficients请求)字段跟DSP请求的相同且Reject Coefficient Value清0,那么请求的系数是接受的,取决于接收机评估的结果,可以考虑作为最后的设置。

- 如果收到2个连续的TS1oS,其中Transmitter Preset(针对preset请求)或者Pre-Cursor, Cursor或者Post-Cursor Coefficient字段跟DSP要求的相同,且Reject Coefficient Value置1,那么请求的系数是被拒绝的,并且不会考虑作为最后的设置。

Downstream Lane EQ phase 3 LTSSM

| 状态跳转 (优先级从上到下) | 跳转原因 |

|---|---|

Recovery.EQ.Phase3 -> Loopback.Entry |

首先需要工作速度是32.0GT/s,变量perform_equalization_for_loopback是1,且满足如下其一: 1. Lane Under Test是工作在最优设置,并且收到2个连续的TS1OS,且Retimer Equalization Extened比特为0 2. 24ms超时后,允许多0到2ms偏差 |

Recovery.EQ.phase3 -> Loopback.Entry |

首先需要工作在64.0GT/s,变量perform_equalization_for_loopback是1b,且满足如下其一: 1. Lane Under Test 工作在最优设置,并且所有lane都收到2个连续的TS1OS,其中Retimer Equalization Extend比特为0 2. 48ms超时,允许超时时间多0到2ms |

Recovery.EQ.Phase3 -> Recovery.RcvrLock |

满足所有: 1. 变量perform_equalization_for_loopback是0且所有配置过的lane都工作在最优配置 2. 当前速度为8.0GT/s或者所有lane都收到2个连续的TS1OS,其中Retimer Equalization Extend为0 |

Recovery.EQ.Phase3 -> Recovery.Speed |

当前速度小于64.0GT/s, 24ms超时,允许超时时间增加0到2ms |

Recovery.EQ.Phase3 -> Recovery.Speed |

当前速度是64.0GT/s时48,允许超时时间增加0到2ms |

当跳转到Loopback.RcvrLock后:

- 如果速度是8.0GT/s,将Link Status 2寄存器中的Equalization 8.0GT/s Phase 3 Successful 和 Equalization 8.0GT/s Complete域置1

- 如果速度是16.0GT/s,将16.0GT/s Status寄存器中的Equalization 16.0GT/s Phase 3 Successful 和 Equalization 16.0GT/s Complete域置1

- 如果速度是32.0GT/s,将32.0GT/s Status寄存器中的Equalization 32.0GT/s Phase 3 Successful 和 Equalization 32.0GT/s Complete域置1

- 如果速度是64.0GT/s,将64.0GT/s Status寄存器中的Equalization 64.0GT/s Phase 3 Successful 和 Equalization 64.0GT/s Complete域置1

当跳转到Recovery.Speed后:

- 变量successful_speed_negotation置0

- 如果当前速率是8.0GT/s,将Link Status 2寄存器中的Equalization 8.0GT/ Complete比特置1

- 如果当前速率是16.0GT/s,将16.0GT/s Status寄存器中的Equalization 16.0GT/ Complete比特置1

- 如果当前速率是32.0GT/s,将32.0GT/s Status寄存器中的Equalization 32.0GT/ Complete比特置1

- 如果当前速率是64.0GT/s,将64.0GT/s Status寄存器中的Equalization 64.0GT/ Complete比特置1

Upstream Lane EQ phase 3

如果速度是64.0GT/s并且从进入该状态以来,所有lane都没有收到2个连续的TS1OS(其中EC为11),则发射机发送TS0OS,其中EC为11b,否则发射机发送TS1OS,其中EC为11b,coefficient设置每条lane独立配置,但是需要遵守如下规则:

- 如果从进入Phase 3以来,收到了2个连续的TS1OS,其中EC为11b,或者是收到了2个连续的TS1OS,其中EC为11b且preset或者coefficients跟最近收到的2个连续TS1OS中的不一致:

- 如果最近连个连续TS1OS中的preset或者coefficients请求是合法且本段支持的

- 将发射器设置更改为请求的preset或coefficients,使新设置在接收器引脚接收到请求新设置的第二个 TS1 有序集结束信号后的 500 ns 内对发射器引脚生效(既必须保持该设置500ns)。发射器设置的更改可能会导致发射器引脚出现非法电压电平或参数,但是非法的电压或者参数持续时间不得超过 1 ns。

- 在传输的TS1Os中,Transmitter Prest字段设置为请求的值(针对preset请求),或者Pre-cursor、Post-cursor coefficients字段设置为发射机的设置(针对Preset请求或者coefficients请求),并且Reject Coefficients Values比特置0

- 否者(preset/coefficients非法或者本段不支持)

- 不会改变发射机正在使用的设置,但是在传输的TS1OS,会将preset或者coefficients值设置为请求的值,并将Reject Coefficients字段置1

- 如果最近连个连续TS1OS中的preset或者coefficients请求是合法且本段支持的

- 否者(进入此状态以后,没有收到两个EC为11b的TS1OS)

- 进入Phase 3时, 最初传输的发射preset可以是当前速度下的Phase 0的preset值,也可以是发射机当前正在使用的发射机preset设置。

Upstream Lane EQ phase 3 LTSSM

| 状态跳转 (优先级从上到下) | 跳转原因 |

|---|---|

Recovery.EQ.Phase3 -> Loobapck.Entry |

perform_equalization_for_loopback是1且当前速度小于64.0GT/s,且满足如下其一: 1. Lane Under Test收到了2个连续的TS1OS,其中EC为00b 2. 32ms超时,允许超时时间增加0到4ms(36ms) |

Recovery.EQ.Phase3 -> Loopback.Entry |

perform_equalization_for_loopback是1且当前速度等于64.0GT/s,且满足如下其一: 1. Lane Under Test收到了2个连续的TS1OS,其中EC为00b 2. 64ms超时,允许超时时间增加0到4ms(68ms) |

Recovery.EQ.Phase3 -> Recovery.RcvrLock |

所有配置过的lane收到2个连续的TS1OS,其中EC为00b |

Recovery.EQ.Phase3 -> Recovery.Speed |

当前速度小于64.0GT/s, 32ms超时,允许超时时间增加0到4ms |

Recovery.EQ.Phase3 -> Recovery.Speed |

当前速度是64.0GT/s时,64ms超时,允许超时时间增加0到4ms |

当跳转到Loopback.RcvrLock后:

- 如果速度是8.0GT/s,将Link Status 2寄存器中的Equalization 8.0GT/s Phase 3 Successful 和 Equalization 8.0GT/s Complete域置1

- 如果速度是16.0GT/s,将16.0GT/s Status寄存器中的Equalization 16.0GT/s Phase 3 Successful 和 Equalization 16.0GT/s Complete域置1

- 如果速度是32.0GT/s,将32.0GT/s Status寄存器中的Equalization 32.0GT/s Phase 3 Successful 和 Equalization 32.0GT/s Complete域置1

- 如果速度是64.0GT/s,将64.0GT/s Status寄存器中的Equalization 64.0GT/s Phase 3 Successful 和 Equalization 64.0GT/s Complete域置1

当跳转到Recovery.Speed后:

- 变量successful_speed_negotation置0

- 如果当前速率是8.0GT/s,将Link Status 2寄存器中的Equalization 8.0GT/ Complete比特置1

- 如果当前速率是16.0GT/s,将16.0GT/s Status寄存器中的Equalization 16.0GT/ Complete比特置1

- 如果当前速率是32.0GT/s,将32.0GT/s Status寄存器中的Equalization 32.0GT/ Complete比特置1

- 如果当前速率是64.0GT/s,将64.0GT/s Status寄存器中的Equalization 64.0GT/ Complete比特置1

感谢您的支持,请扫码打赏